2. 中国人民大学 信息学院, 北京 100872;

3. 清华大学 计算机科学与技术系, 北京 100084;

4. 北京大学 信息管理系, 北京 100871

2. School of Information, Renmin University of China, Beijing 100872, China;

3. Department of Computer Science and Technology, Tsinghua University, Beijing 100084, China;

4. Department of Information Management, Peking University, Beijing 100871, China

近些年, GPU由于具有高并行性的特点, 在高性能计算等领域得到了充分的应用.然而, 由于GPU特有的以线程组SIMT的执行方式执行指令, 对访存方式有较高的要求.通常, 越规则、密集的计算任务越容易发挥GPU的硬件性能, 反之性能较弱; 同时, GPU的内存和CPU的内存是分离的, 对于大数据应用, 有限的内存容量和经过PCIe的数据传输也是影响GPU可用性的一大挑战.针对这一问题, 硬件设计厂商推出了将CPU和GPU集成在一个芯片的异构融合处理器, 兼顾两者优点.例如, AMD公司在2011年推出了APU处理器[1], Intel公司在2012年推出了带有集成GPU的处理器[2], 而Nvidia公司也在2014年推出了Tegra处理器[3].这种异构融合架构能够同时结合CPU和GPU的体系结构特征, 对异构计算进行了扩展, 为高性能计算等领域带来了新机会[4, 5].

和普通的离散GPU设计相比, 异构融合处理器具有诸多优势.

● 第一, CPU和GPU能够共享内存, 这种共享内存的设计可以避免CPU和GPU间通过PCIe进行数据传输.Intel公司还推出了CPU、GPU共享缓存的异构融合处理器[3], 使不同设备间的通信更高效.

● 第二, CPU和GPU可以访问同样的数据, 这样CPU和GPU可以有更多的交互.

这些优势使得异构融合处理器具有更广泛的应用前景, 但如何利用好异构融合处理器仍充满挑战:首先, 异构融合处理器还处于发展阶段, 许多设计并不完善; 其次, 充分发挥异构融合处理器的性能需要对CPU和GPU进行不同的体系结构优化, 并且需要考虑额外的多设备任务分配, 这增加了异构融合处理器的编程难度; 再次, 异构融合处理器上相集成的设备具有多样性, 不仅局限于GPU, CPU设备的集成.例如, 目前也出现了FPGA和CPU相集成的异构融合处理器.FPGA著名生产厂商Altera被Intel公司收购后也推出了FPGA-CPU相融合的处理器[6], 将FPGA和CPU集成在一起, 能够使FPGA和CPU更好地交互.

面对这些挑战, 为了更充分地利用异构融合处理器, 首先需要对其进行性能分析, 充分理解异构融合处理器的行为.目前, 对异构融合处理器的利用方式可以分为单程序独占异构融合处理器利用不同设备特点运行以及多程序在异构融合处理器上混合运行.其中, 对于单程序的运行, 并不是在所有情况下同时使用多种设备混合运行可以达到最优的性能结果.实验表明, 对于CPU、GPU相集成的异构融合处理器, 根据程序的性能表现大体可分为4类:利用异构融合处理器上的多种设备混合执行能够带来加速效果的程序、GPU主导型程序、CPU主导型程序和无设备倾向型程序[7].每种程序类型都具有不同的性能特征[8], 例如, 多种设备混合执行能够带来加速效果的程序不需要较高的带宽; 而只使用GPU设备达到最佳性能的GPU主导型程序有高并行度等特点, 这样可更充分地利用GPU资源, 包括计算处理单元和可控制的局部存储等; 而CPU主导型程序具有低并行度等特征[7].而对于多程序在异构融合处理器上的混合运行, 存在性能降级, 影响因素也更复杂.研究表明, 操作系统的上下文切换在多程序混合运行中起了关键作用[9, 10].目前, 不同程序多设备混合运行性能降级的主要原因在于CPU内的竞争, 而不是对内存带宽的竞争; 操作系统中的上下文切换策略对混合运行中的GPU性能影响较大, CPU主机端部分的GPU控制线程是混合运行性能降级的主要原因.此外, 功耗也是处理器设计的一个重要指标.目前, 异构融合处理器通常具有低功耗的特性.

基于对异构融合处理器性能特征的理解, 编程时可从异构融合处理器所引入的新特性、设备体系结构特征等方面进行优化, 具体可分为针对不同设备进行数据访问方式调整、并行粒度优化、使用局部存储的方式调整等[11].同时, 将负载向异构融合处理器的具体设备分配时, 有多种优化策略进行选择.Zhang等人[11]提出了在异构融合处理器上基于建模的方法混合运行CPU、GPU设备:首先, 使CPU处理一部分负载, 记录时间, 并预测CPU的处理速度; 之后, 用同样的方法预测GPU的处理速度; 在获得CPU、GPU的测试性能后, 对剩余负载依据CPU和GPU的性能对比进行划分.Pandit等人[12]研究了不需要采样就可以同时混合运行离散GPU和CPU的方法, 这一方案对任务的分配是通过OpenCL编程中的workgroup[13]在CPU和GPU端的分配完成的.目前, 也有关于异构融合处理器功耗优化的研究工作.Zhu等人[14]研究了在异构融合处理器上如何混合运行多个程序, 使处理器运行的功耗较低.这项研究从功耗的角度进行了分析, 并提出了相应混合运行调整策略.Garzón等人[15]针对迭代计算提出了异构融合处理器上的功耗优化方案E-ADITHE, 该方案包含启发式的方法, 基于功耗预测选择合适的处理设备, 同时也会考虑异构处理器内部的负载均衡特性.此外, 异构融合处理器正被用于越来越多的领域, 结合具体的应用, 异构融合处理器往往具有更多的优化空间.

通过对以往研究工作的总结, 本文对异构融合处理器研究的未来发展方向进行了展望:首先, 结合异构融合处理器不断演变的发展过程, 未来的异构融合处理器会集成更多的计算核心, 性能和稳定性等方面也会增强, 可用于高性能计算机的设计; 其次, 对于异构融合处理器, 目前需要针对不同设备进行程序优化才能使其达到较优的性能, 编程要求较高, 未来的异构融合处理器可能会集成更多种类的设备, 编程情况会更复杂, 而这些情况会促使新的编程语言设计和辅助工具出现; 再次, 对于大数据类数据密集型应用, 由于异构融合处理器具有共享内存等特征, 会有越来越多的大数据应用利用异构融合处理器进行处理.而对于机器学习等新型计算密集型应用, 异构融合处理器集成了不同的设备特性, 对于特定机器学习应用会有新突破.

本文第1节对异构融合处理器的体系结构特征和编程语言进行介绍.第2节从研究方向、成果表现等方面对以往相关工作进行分类与汇总.第3节对异构融合处理器上的性能分析类工作进行总结.第4节进一步对涉及异构融合处理器的优化工作进行汇总.第5节对异构融合处理器的具体应用也进行介绍.第6节对异构融合处理器未来的研究方向进行展望.最后, 第7节对全文进行总结.

1 异构融合处理器概述本节主要对异构加速器件和异构融合处理器进行基本情况介绍, 包括异构加速器件简介、体系结构特征和编程语言.

1.1 异构加速器件随着信息技术的发展, 需要处理的数据量增大, 来自科学计算等领域的应用需求的复杂性也进一步增大, 传统CPU无法满足大量的计算需求.目前, 常见的解决方案是在系统中增加GPU等异构加速器件, 这样可以在对系统改动较小的情况下, 极大地增加系统的处理能力.配有异构加速器件的计算系统通常由两部分构成:主机端和异构加速器件端.通常, 主机端由通用CPU构成, 异构加速器件端体现系统的主要计算能力.异构加速器件具有多种选择, 如GPU、Xeon Phi、FPGA等, 目前最为流行的加速器件是GPU.GPU是由大量并行处理单元构成的, 这些处理单元包括了上千个轻量级的计算核心.这些轻量级的计算核心可以访问共同的全局内存, 单个并行处理单元包含的计算核心具有各自独立的局部存储.异构加速器件常见的编程语言包括OpenCL[13]和CUDA[16], 在编写程序过程中, 需要对异构加速器件的体系结构有所了解; 目前也存在更高层的编程工具, 如Matlab等, 但这些工具通常无法充分发挥异构加速器件性能.

对于离散的异构加速器件, 需要将数据从主机端传输到异构加速器件的内存中, 数据计算完成, 再将结果传输回主机端.数据传输会引起时间开销, 这种主机端和异构加速器件之间的交互对于计算系统性能影响很大, 因此在离散架构存在的同时, 出现异构融合架构, 将异构加速器件与主机端集成在一个芯片上, 构成异构融合处理器, 共享内存等资源, 避免了数据传输开销.但异构融合处理器的实现具有诸多挑战, 例如如何有效利用芯片面积, 如何解决芯片功耗密度上升问题等.

1.2 体系结构尽管异构融合处理器的设计具有诸多挑战, 目前仍出现了一些异构融合架构, 如AMD公司的Carrizo[17]、Intel公司的Skylake[18]和Nvidia公司的Denver[19]等.图 1以CPU、GPU相集成的异构融合处理器为例进行了展示, 图 1中的异构融合处理器分为CPU部分和GPU部分, 这两部分可访问同样的内存.CPU部分具有L1和L2等多级缓存结构, 不同型号的CPU略有不同.例如, AMD公司生产的A10-7850K异构融合处理器的CPU部分具有共享的L2缓存, 而Intel公司生产的i7-4770R异构融合处理器则采用私有L2缓存设计.对于GPU部分, 不同硬件厂商生产的GPU存在较大的体系结构差异, 包括局部存储和缓存设计等方面.例如, 相比于A10-7850K异构融合处理器, i7-4770R异构融合处理器上存在共享L3缓存.此外, 部分异构融合处理器上出现了多设备共享缓存和嵌入式存储(embedded DRAM, 简称EDRAM)等结构.对于共享内存访问, 目前对CPU和GPU等设备提供的带宽不一样[20].

目前, 针对异构融合处理器的研究工作都是围绕上述类型体系结构展开的.研究者围绕多设备相集成的特点结合应用在异构融合处理器上, 进行各种性能分析与优化.由于异构融合处理器将不同设备集成在一起共享内存, 和离散架构相比需要考虑更多因素, 如多设备间如何保证内存一致性等问题.异构融合处理器共享内存的特性避免了通过PCIe的数据传输, 但也增加了不同设备维护共享内存一致性的开销[21].

关于异构融合处理器的共享缓存, Yang等人[22]提出了在GPU运行时使CPU进行辅助预取的工作:首先, 从GPU需要运行的程序中抽取出和内存访问相关的地址计算指令, 增加CPU循环操作准备为不同的线程预取数据; 其次, 当GPU程序开始运行时, CPU提前运行预先抽取出的内存操作指令, 使GPU需要访问的数据提前存入缓存.为了保证CPU预取的有效性, 通过观察缓存缺失率改变循环迭代的步长.此外, 对于CPU、GPU异构融合处理器, GPU的高吞吐率会使CPU的一致性维护开销较大.Power等人[23]提出了基于目录结构的针对CPU, GPU异构融合处理器的一致性协议(heterogeneous system coherence, 简称HSC), 为CPU和GPU的L2缓存开设局部存储区, 用来记录被CPU或GPU控制的区域.这种设计的空间开销小, 同时也比传统的块级目录方法简单.由于维护CPU和GPU间的缓存一致性存在开销, Agarwal等人[24]提出了选择性缓存策略(selective caching), 使GPU不缓存需要维护一致性的数据, 降低共享缓存所带来的负担.

继CPU, GPU相集成到一个芯片后, 各处理器生产厂商也相继推出了CPU、FPGA相集成的异构融合处理器.例如, Intel公司设计了使用快速通路(quick path interconnect, 简称QPI)替换PCIe连接的CPU-FPGA集成方案. Choi等人[25]分析、对比了通过PCIe与CPU相连接的离散FPGA和通过QPI与CPU连接的FPGA性能, 指出:通过快速通路相集成的CPU-FPGA方案在细粒度通信等方面具有更低的延迟, 而FPGA_DRAM的重用率决定这两个平台的最大有效带宽.通过高效的设计, 使用PCIe连接的CPU-FPGA平台能够在很多方面达到和使用QPI平台类似的效果.同时, 该研究指出:目前, 通过PCIe连接和通过QPI连接的方式都有较大的性能提升空间.这一研究可以为CPU-FPGA异构融合处理器的未来设计提供参考.对于大数据应用, Cong等人[26]进一步提出了数据流执行模型和FPGA, CPU间的调度算法, 该方案能够使CPU和FPGA间更好地进行交互, 提升系统整体资源利用率.

1.3 编程语言异构融合处理器的编程语言主要选用OpenCL并行编程语言[13], OpenCL可控制异构融合处理器上的多种设备.相比于Pthreads[27]、OpenMP[28]、CUDA[16]等语言, OpenCL的主要优点在于所支持的硬件设备的广泛性.自Khronos小组2009年公布OpenCL编程标准后, 各大硬件设备生产厂商纷纷支持OpenCL的编程标准, 开发了各自硬件产品相应的OpenCL编程库.因此, 可以用OpenCL控制绝大多数设备, 如CPU、FPGA和GPU等设备, 这是其他的并行编程语言所无法做到的.目前, 异构融合处理器上的相关编程工作也主要以OpenCL的编程为基础进行.

OpenCL的编程流程较为复杂, 首先需要建立程序所需要的上下文环境(context), 并在上下文环境中创建设备(device), 如异构融合处理器中的CPU和GPU等; 其次, 需要为不同的计算设备建立相应的命令队列(command queue), 用于运行所需的计算核心(kernel); 再次, 需要分配资源, 指定具体的线程组织方式.OpenCL中以线程组(workgroup)的形式对线程进行组织, 并将线程视为工作项(workitem).

最后, 通过OpenCL的clEnqueueNDRangeKernel(·)函数发射计算核心到相应设备的命令队列中进行运算, 获得结果, 并显式释放资源.在OpenCL的计算核心运行过程中, 一个线程组只可在同一设备所提供的计算单元(computing unit)中执行, 而线程组内的线程可通过局部存储(local memory)和屏障操作(barrier)进行组内交互和同步.OpenCL中不存在所有线程的屏障同步操作.此外, OpenCL提供clFush(·)函数, 可确保设备命令队列中的指令发射到了相应设备, 而clWaitForEvents(·)函数可用于确保完成全部命令.

2 研究概况本节对过往针对异构融合处理器的研究进行了总结.通过对所有涉及异构融合处理器的研究进行整理, 表 1列出了近年来关于异构融合处理器的研究汇总, 概括地描述了这些研究工作的方向和研究内容.研究方向分为异构融合处理器的性能分析、异构融合处理器的性能优化和异构融合处理器的具体应用实例.其中, 性能分析是研究的基础, 在充分了解异构融合处理器特性的基础上, 进一步探索各类优化技术, 最后, 将异构融合处理器使用在各领域的应用实例中.表 1中具体成果表现又可进一步细分:性能分析类研究可进一步细分为单程序运行性能分析、多程序运行性能分析和涉及处理器功耗的相关分析研究; 涉及性能优化的研究目前可分为体系结构优化、负载划分与调度优化以及针对处理器功耗的优化; 而异构融合处理器的具体应用目前主要涉及科学计算和数据科学领域.表 1同时列出了论文标题、发表年份、作者信息、研究内容概括和在本文中的引用编号.

| Table 1 Summary of related papers 表 1 相关论文总结 |

图 2描述了表 1中各方向的论文分布情况:性能分析类论文有16篇; 性能优化类论文有14篇, 主要集中在不同设备间的负载划分与调度优化; 涉及具体应用实例的论文有23篇.目前, 基于异构融合处理器的应用多集中在数据科学领域和科学计算领域, 但随着近年来机器学习技术的发展, 研究者开始考虑如何将异构融合处理器应用于机器学习领域, 如深层神经网络训练的加速等环节.虽然目前这个领域的研究较少, 但具有较大的发展潜力.此外, 也有研究者提出了利用异构融合处理器对网络数据包进行处理的解决方案, 这也是一个异构融合处理器潜在的应用方向.

|

Fig. 2 Amount of papers in each category 图 2 各领域的论文数量 |

图 3描述了各研究方向的论文随时间线的增长图.从图中可以看出, 关于异构融合处理器的研究从2010年开始快速增加, 这与计算机技术的发展密切相关.正是在2010年前后, AMD宣布推出集成CPU和GPU的异构融合处理器, 以此为契机, 关于融合处理器的研究开始被大量研究者作为研究课题.到目前为止, 关于异构融合处理器的性能分析优化和基于异构融合处理器的应用是这个领域的热点方向.

|

Fig. 3 Trends in the number of papers 图 3 论文数量增长趋势 |

对于表 1中的应用, 为了进一步分析这些应用和优化技术间的关系, 本文将各应用对体系结构优化、负载划分与调度优化和功耗优化的利用情况总结见表 2, 发现所有应用都会结合异构融合处理器中的异构设备进行体系结构的优化.23个应用中, 有10个应用针对不同设备进行了负载划分与调度优化, 超过半数的应用仅使用了异构融合处理器上的加速设备, 没有考虑对CPU的利用情况.这些研究证明, 仅使用异构融合处理器上的加速设备也可以带来性能加速效果, 性能提升的主要因素在于避免了CPU和异构设备间的数据传输开销.此外, 表 2还说明, 目前绝大多数应用主要考虑系统的计算能力, 考虑功耗方面的优化较少.随着异构融合处理器的性能不断提升, 以及由异构融合处理器搭建的低功耗集群越来越常见, 预计未来会有更多应用研究将功耗作为优化指标出现.

| Table 2 Summary of optimization methods used in each research work 表 2 各研究工作所用优化方法汇总 |

3 异构融合处理器的性能分析

性能分析是体系结构研究的一个重要方面, 可以帮助理解计算机的行为表现.本节主要介绍异构融合处理器的性能分析工作, 分为单程序在异构融合处理器上利用多设备运行的性能分析研究、多程序同时在异构融合处理器上混合运行的分析研究以及异构融合处理器上的功耗分析研究.

3.1 单程序运行性能分析单程序运行的性能分析指分析一个程序在异构融合处理器的不同设备混合运行时的性能表现.

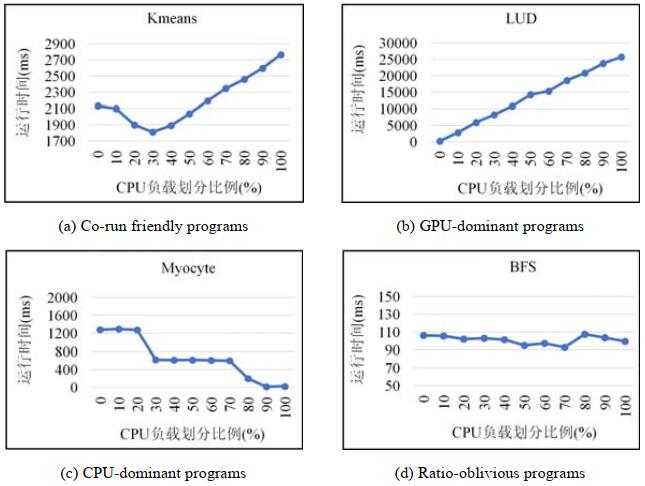

Zakharenko等人[31]利用模拟器对CPU, GPU相融合的处理器进行分析, 模拟出Rodinia基准测试程序集在异构融合处理器上的性能收益.Zhang等人[8]对CPU-GPU异构融合处理器上的程序运行结果进行了分析, 将程序分为4种类型:(1)多种设备混合运行能够带来性能收益的程序(co-run friendly programs); (2)仅运行GPU可获得最佳性能的GPU主导型程序(GPU-dominant programs); (3)仅运行CPU可获得最佳性能的CPU主导型程序(CPU-dominant programs); (4)对不同设备进行负载划分程序性能差异不大的无倾向型程序(ratio-oblivious programs).这4种程序类型的性能表现如图 4所示.

其中:多种设备混合运行获得性能收益的程序具有相对长的运行时间(计算核心的开启时间开销可忽略), 且对带宽的要求不高; 而GPU主导型程序常包含关于局部存储(local memory)的使用与优化, 且有高度并行性; CPU主导型程序的并行度不高, 运行时间可能不长, 尽管CPU的计算性能远低于GPU, 但在这些情况下, GPU无法充分发挥其强大的计算能力; 无倾向性程序的性能瓶颈常在于内存访问带宽, 或所选择的计算核心执行时间占比相对低, 这样对不同设备进行负载划分, 异构融合处理器的性能表现差异不显著[7].

对于不规则负载在CPU-GPU异构融合处理器上的处理, Zhang等人[32]进一步分析指出:对于不规则负载运行时需要考虑更多的细节, 因为GPU和CPU对不规则负载的敏感程度不同.以稀疏矩阵为例, 令稀疏矩阵每行中非零元素数目变化的方差表示负载的不规则程度, 对于大量具有不同不规则程度的矩阵, 随着不规则程度的增加, GPU性能表现出了明显的下降趋势; 而相应的CPU性能没有类似趋势.因此, CPU对负载的不规则变化不如GPU敏感, 在异构融合处理器上对不规则负载进行程序优化时需要结合不规则负载特性.Zhang等人[33]在异构融合处理器上对稀疏矩阵计算程序和图算法程序进行了对比, 指出:图程序通常计算模式更为复杂, 计算过程可包含多伦迭代, 且每次涉及不同的子图的部分, 具有动态特征, 需要进一步优化.

Spafford等人[30]对异构融合处理器的缓存和内存使用情况进行了研究, 分析吞吐率和延迟, 还在CPU对内存不断访问的情况下对GPU的程序运行进行分析, 并指出, 目前异构融合处理器在资源配置管理等方面存在提升空间.异构融合处理器具有共享内存的特性, Daga等人[29]设计了基准测试程序集进行测试, 包括数据传输程序、计算核心函数、真实应用场景等, 实验结果表明, 异构融合处理器和离散的GPU相比在数据传输方面有明显的优势.Dashti等人[21]指出, 异构融合处理器中不同设备维护共享内存一致性存在开销.Lee等人[20]分析了AMD Llano异构融合处理器上的不同设备访问内存的读写带宽情况.OpenCL语言中可以使用不同关键字声明数组的类型, 如主机端(host buffer)类型、设备端(device buffer)类型, 这一研究结果表明, CPU、GPU读写主机端和设备端数据时具有不同的性能表现.在异构融合处理器程序设计时要充分考虑这些因素.

3.2 多程序的性能分析研究者也关注如何在异构融合处理器的不同设备上运行不同程序.Zhu等人[9, 10]研究让两个程序分别运行在异构融合处理器的CPU和GPU设备上, 分析和单个程序运行在处理器上相比的性能下降情况.这一研究首次指出, 操作系统的上下文切换在多程序混合运行中起了关键作用.研究的主要发现包括:(1)不同程序多设备混合运行性能降级的主要原因在于CPU内的竞争, 而不是内存的竞争; (2)操作系统中, 上下文切换策略对混合运行的GPU性能影响较大; (3) CPU主机端部分的GPU控制线程是混合运行性能降级的主要原因; (4)数据拷贝对性能有轻微影响; (5)操作系统的功耗管理对GPU的性能也有潜在的影响.最后, 这一研究提出了异构融合处理器设计新的管理方案.

部分异构融合处理器存在CPU、GPU共享的缓存(shared last-level cache), Mekkat等人[34]研究了不同类型程序在CPU、GPU设备上混合运行对缓存的影响, 研究指出:由于GPU具有远多于CPU的硬件线程, 在目前的缓存管理策略中, 如果存在多程序运行, 运行在CPU上的应用对共享缓存的利用会被运行在GPU上的应用干扰, 对于缓存敏感型程序性能降级明显.而对于GPU, 大部分应用具有足够的并行度, 能够容忍由于共享缓存访问缺失所带来的访存延迟.该研究进一步提出了异构缓存管理策略(heterogeneous LLC management, 简称HeLM), 能够利用GPU对访存延迟不敏感的特性, 阻止GPU对共享缓存的访问, 以腾出更多的缓存空间供CPU使用.

3.3 功耗分析功耗是评估异构融合处理器的另一重要指标, 许多硬件厂商如AMD和Intel将异构融合处理器视为性能和功耗的折中方案.Zhang等人[8]对异构融合处理器进行了功耗分析, 并和离散的GPU进行了比较.研究指出:对于运行同样的程序, 并非在所有情况异构融合处理器均可能耗最少.因为目前同一时期的异构融合处理器计算能力往往低于离散GPU, 尽管在程序运行过程中异构融合处理器具有较低的功率, 但运行时间也更长, 耗能也可能更高.Said等人[35]以三维声学处理程序为例, 在单机和集群环境中对CPU-GPU异构融合处理器和离散的CPU, GPU设备进行对比.实验表明:异构融合处理器的性能介于CPU和GPU两者之间, 但功耗更低.普通CPU处理器中存在功耗控制, 用于使处理器具有低功耗开销和更高可靠性.Zhu等人[14]对异构融合处理器的功耗控制机制进行了分析, 首次指出:异构融合处理器需要考虑两种及以上类型的设备, 处理器对功耗控制更敏感.异构融合处理器多种设备紧密结合的设计会带来更多的内存竞争, 也会影响到功耗限制.Dávila等人[36, 37]研究了负载划分对功耗和性能等的影响, 并指出两者间的相关性.

3.4 小结性能分析是进一步优化程序的基础.对程序进行性能分析, 可探明程序在不同情况下的性能表现, 分析异构融合处理器对于不同类型程序的性能瓶颈, 如多设备混合运行是否能够获得性能提升等, 从而进一步优化程序, 提升程序在异构融合处理器上的性能.本节从单程序的性能分析、多程序的性能分析以及功耗角度对异构融合处理器的运行进行了介绍.对于单程序的性能分析, 当内存带宽利用情况不紧张时, 可以考虑增加计算设备更充分利用系统资源; 对于多程序混合运行, 在目前操作系统层缺少相应优化设计, 多程序混合运行效果不理想; 在功耗方面, 异构融合处理器整体功耗低于离散GPU功耗, 但由于性能等方面限制, 优势不明显.研究表明, 目前的异构融合处理器仍不成熟, 具有很大的发展空间.

4 异构融合处理器上的优化工作在充分理解异构融合处理器的性能表现的基础上, 本节主要介绍针对异构融合处理器的优化工作.

4.1 体系结构优化Barik等人[38]首次考虑在异构融合处理器运行不规则负载时, 如何将负载从CPU端迁移到GPU端.实验结果表明, 大部分的程序都能获得性能受益.但这一研究主要使用了异构融合处理器的GPU设备, CPU端存在资源浪费.Zhang等人[11]以GPU-CPU异构融合处理器为例, 详细介绍了异构融合处理器上不同设备混合运行的性能优化技巧, 具体包括不同设备体系结构的相关优化、内存带宽的利用以及不同设备运行时计算核心的重叠情况等.其中, 体系结构的优化可以分为针对异构融合处理器的不同设备进行数据访问方式调整、并行粒度优化、使用局部存储的方式调整等[7].图 5是局部存储优化和访存优化的程序示例.Streamcluster来自于Rodinia[68]基准测试程序集.图 5(a)表示的计算核心更适合GPU运行, 图 5(b)表示的计算核心更适合CPU运行.首先, GPU存在局部存储, 但CPU没有, 因此对于使用局部存储的数组coord_s, CPU计算核心需要直接对全局内存中的相应数据进行操作, 避免与局部存储相关的访问.如在图 5(b)中, 没有出现关键字__local.其次, CPU和GPU的最优访存方式不同, GPU适合同一线程组内的多个线程同时访问相邻的数据.如图 5(a)中, 线程组中的线程访问的是相邻的数据, 而CPU适合各独立线程访问的数据是相邻的, 这样缓存局部性更好.因此, 在图 5(b)中添加了coord_d所表示的矩阵的转置数组coord_d_cpu.CPU单线程对coord_d_cpu数组的访问连续, 具有较好的局部性.通过这些优化技术, 不同设备均可实现高效的内存数据访问.

图 6是对并行度和循环优化的例子, 代码来源于Rodinia程序集高斯消元程序, 通过调整并行粒度和循环优化来增加局部性.图 6(a)表示的计算核心适合GPU运行, 图 6(b)表示的计算核心适合CPU运行.图 6(b)中的计算核心相比于图 6(a)中的计算核心降低了线程维度, 减少了线程数量; 且保证对于a_dev数组, CPU中每个线程能够实现连续访问, 具有较好的数据局部性, 这有助于CPU缓存发挥作用.

对于内存带宽的因素, 由于多种设备访问同样的内存, 因此需要减少设备对内存带宽的影响.例如, 尽可能把数据缓存在GPU的局部存储.同时, CPU和GPU设备运行计算核心的时间重叠情况也会影响混合运行的性能, 运行时间长的计算核心更容易重叠; 对于运行时间短的计算核心, 多设备混合运行获得的性能提升有限.许多相关研究是通过对上述因素进行优化, 提升系统性能.

4.2 负载划分与调度优化本节主要介绍针对异构融合处理器中不同设备的负载划分与调度优化工作.异构融合处理器存在多种设备, 如何使多种设备能够混合运行, 一直是融合处理器的研究热点.

Kallem等人[39]研发了面向异构融合处理器的调度方案, 该方案首先抽取一部分负载交由异构融合处理器上的GPU处理, CPU继续处理后续负载.在GPU处理完成所分配的负载后, 计算CPU和GPU所处理负载量的比例, 进而获得CPU和GPU处理能力上的差异.之后, 根据CPU和GPU处理数据能力的不同, 对剩余负载进行重新划分.假设GPU所分得的负载比重为ag(0≤ag≤1), 则剩下1-ag的负载将分配到CPU.在理想情况下, 异构融合处理器上的不同设备能够同时结束对各自负载的处理, 实现负载均衡.

Zhang等人[11]提出在异构融合处理器上基于建模的方法混合运行CPU、GPU设备.首先, 使CPU处理一部分负载, 记录时间, 并预测CPU的处理速度; 之后, 用同样的方法预测GPU的处理速度.在获得CPU、GPU的测试性能后, 对剩余负载依据CPU和GPU的性能对比进行划分.这一方法的缺点在于:提升预测性能的准确性需要增加CPU、GPU处理负载的采样量, 但这样真正用于CPU、GPU混合处理的负载量就减少了; 并且对于不规则负载, 很难通过简单采样直接预测整体性能.同时, 对于动态负载, Zhang等人[43]进一步提出了实时细粒度负载划分算法, 充分利用系统资源.

Pandit等人[12]研究不需要采样就可以同时混合运行离散GPU和CPU的方法, 这一方案也适用于异构融合处理器.该方案对任务的分配是通过workgroup(OpenCL术语)在CPU和GPU端的分配完成的.CPU和GPU端同时运行计算核心, 首先, 通过数据传输命令将数据部署到CPU和GPU设备上.在GPU端, 开启所有的线程组, 每组内设置一个线程接收CPU端的状态, CPU端的运行划分为许多子计算核心.该方案对负载进行编号, 根据编号使GPU从负载最前端向后处理, CPU从后向前处理.当CPU处理完成每个子计算核心后, 就将数据和状态发送给GPU.当GPU执行到某时刻, 发现将要处理的数据CPU已经处理完成时, GPU停止计算.之后, GPU进行数据整合, 并将处理结果传回CPU.Pandit等人[12]在异构融合处理器上实现了这一方案, 实验表明存在一定开销. Tang等人[40]在异构融合处理器的资源分配方面设计了多种资源公平分配策略, 这一策略引入了博弈论中的公平性法则, 在异构融合处理器资源分配中同时考虑公平性和效率, 并在两者间进行平衡.

并行环境中, 异步的任务可以描述为有向无环图.Puthoor等人[41]针对异构系统架构研究这一算法, 可以细粒度地进行任务管理.FinePar[32]是首个针对不规则负载的多设备混合运行细粒度负载划分框架, 能够同时利用多种设备.以往针对异构融合处理器的划分算法没有考虑GPU和CPU的体系结构特点以及负载内部的不规则性, 不能完全适应不规则负载.FinePar使用离线训练的方式建立性能模型, 能够依据给定负载的不规则程度模拟出CPU和GPU的性能.之后, 对于用户提供的程序和不规则负载, 能够自动修改代码, 把负载中相对规则的部分分配给GPU, 剩下部分分配给CPU.因为GPU对负载的不规则性较为敏感, 这种方法能够最大化GPU性能, 进而提升异构融合处理器的整体性能.Cho等人[42]进一步实现了实时的不规则负载划分策略.

4.3 功耗优化方法在高性能计算领域, 功耗是评价计算机系统的一项重要指标.AMD和Intel等硬件厂商将异构融合处理器作为平衡性能和能耗的设计, 可以提供更好的性能功耗比[44, 69].Gu等人[45]在异构融合处理器上对多层感知神经网络进行加速, 并从性能功耗比的角度展示异构融合处理器的优势.Zhu等人[14]研究在异构融合处理器上如何混合运行多个程序使处理器运行的能耗较低, 这项研究从能耗的角度进行了分析, 并提出了相应混合运行调度策略:首先, 通过不同频率下的模型判断程序混合运行是否可以从混合运行中受益, 记录受益最大的结果; 之后, 将混合运行结果和最高频率下的单设备运行结果进行比较, 并选择最优策略.Garzón等人[15]针对迭代计算提出了异构融合处理器上的功耗优化方案E-ADITHE, 该方案包含启发式的方法, 基于功耗预测选择合适的处理设备, 同时也会考虑异构处理器内部的负载均衡特性.

4.4 小结异构融合处理器将多种设备集成到一个芯片上, 目前, 优化工作主要依靠编程人员实现.本节对异构融合处理器上的优化工作进行了总结.在内存带宽允许的情况下, 可进行多设备混合运行充分利用系统资源; 此外, 当应用可拆解为不同部分时, 可考虑各部分在不同设备的性能表现, 将各部分运行在异构融合处理器上最适合的设备.在程序优化的过程中, 由于不同设备间的体系结构差异巨大, 需要对不同设备的代码分别进行优化; 同时, 异构融合处理器也具有以往离散架构所没有的特性, 如共享内存、多设备异步执行等, 因此在优化的过程中, 还需考虑这些新特性.接下来将对异构融合处理器在其他领域的具体应用进行介绍.

5 异构融合处理器的应用多设备融合设计和以往离散的设计相比具有更多的优化机会, 目前已被应用于越来越广泛的应用之中.本节主要对异构融合处理器上的具体应用场景进行介绍.

5.1 数据密集型应用异构融合处理器可以在数据库等领域进行性能加速, 目前, 有学者研究异构融合处理器在大数据管理中的使用.Hetherington等人[46]评估了键值存储在异构融合处理器上的性能表现, 和使用离散的GPU、CPU架构相比, 异构融合处理器能够带来较大的性能提升.针对在线分析处理, He等人[50]提出了在异构融合处理器上基于缓存的查询算法, 使CPU辅助GPU缓存数据, 提升GPU查询的缓存命中率.在大数据管理领域, He等人[49]首先提出了利用异构融合处理器完成数据库查询操作中的哈希合并(Hash join)操作.由于合并操作可以分为建立、探测等步骤, CPU和GPU设备在不同步骤中有不一样的性能表现.这一研究在各步骤中考虑异构融合处理器中的CPU、GPU特性, 合理分配负载混合处理.DIDO[52]是异构融合处理器上的内存键值存储系统, 系统在GPU、CPU设备间实现了pipeline动态执行模型, 能够自适应地将不同负载动态地在运行时分配给GPU和CPU设备.Daga等人[47]在异构融合处理器上研究B+树的实现.B+树是数据库领域中索引的基础操作, 这一工作针对其访问的不规则特性和CPU、GPU间的数据传输进行优化.FineStream[53]是首个利用异构融合处理器实现的SQL流处理系统, 查询语句可分解为多个算子, 不同算子对异构融合处理器的设备有不同的性能偏好.FineStream建模将不同的算子分配在异构融合处理器的不同设备上, 并考虑了共享内存带宽等特性, 实现了细粒度地流处理多设备混合运行.

MapReduce[70]是一个用来处理大规模数据集的并行编程模型, 将对数据的处理抽象成Map(映射)和Reduce (归纳)两个阶段.用户只需要按照给定的Map和Reduce接口编写程序, MapReduce编程模型就会自动对数据进行划分和调度, 并行处理数据, 用户不需要对其进行控制.这样的编程方式极大地降低了用户的编程难度.异构融合处理器将CPU与多种设备相集成, 不同设备体系结构差异较大, 需要有针对性地进行细粒度复杂优化, 以发挥不同设备的潜在性能, 这无形中增加了异构融合处理器的使用门槛.Chen等人[48]首先在异构融合处理器上实现了MapReduce框架, 能够对用户屏蔽异构融合处理器的底层细节, 用户只需按照给定的接口编写程序, 系统就能自动在不同设备上分配、处理负载.在该框架的划分策略中, 调度器将输入任务分配到各worker, 所有worker (MapReduce术语)都执行同样的步骤.每个worker都是一个workgroup(OpenCL术语), 由一组线程构成, 可存在于主机端也可存在于异构设备端, 分配到worker的任务会均匀分配到其中的所有线程一起处理.MapReduce是迄今应用最广泛的数据并行编程框架之一, 尽管MapReduce框架存在扩展性和容错方面的实现开销, 仍有大量关于提升MapReduce计算性能和降低功耗的研究, 这些研究涉及异构器件通常会使用离散GPU.功耗是大规模集群计算考虑的重要指标, 由于异构融合处理器具有低功耗的特性, Kim等人[51]首先从功耗角度研究在由异构融合处理器搭建的集群上运行MapReduce框架.这一研究使用Intel异构融合处理器, 通过修改Hadoop的通用机器学习库Apache Mahout[71]使其支持运行.通过进一步优化异构融合处理器的新特性, 如对共享内存、缓存等方面进行优化, 证明了异构融合处理器在集群计算功耗方面的巨大优势.

5.2 计算密集型应用研究者将异构融合处理器用于科学计算领域, 结合具体应用进行优化.本节选择其中代表性的应用进行介绍.Doerksen等人[54]研究在异构融合处理器上如何进一步提升科学计算程序性能, 并以高斯消元程序和0-1背包问题求解程序为例进行研究.该研究工作将GPU用于计算, 而CPU只用于检查结束条件和同步等操作. Delorme等人[56]在异构融合处理器上实现了并行快速排序算法, 将算法分为了局部排序、局部分析、排名、分发等4个阶段, 在各阶段分别考虑CPU和GPU处理负载的不同部分, 共同执行程序.Eberhart等人[59]研究异构融合处理器上的Stencil计算.Stencil计算负载大部分较为规则, 适合GPU并行处理, 但仍存在一些边缘的不规则部分.这一研究利用CPU、GPU共享内存的特点, 令CPU负责处理Stencil中的边缘部分, GPU处理规则部分, 使程序达到了较高性能.Daga等人[58]研究了广度优先搜索算法在异构融合处理器上的实现.广度优先搜索算法常见的遍历包括自上而下的遍历和自下而上的遍历两种, 其中:自上而下的遍历算法适合CPU, 自下而上的算法适合GPU.这一工作利用共享内存的特征, 在算法执行的过程中选择合适算法, 并在不同设备间进行切换.Zhang等人[62]进一步提出了异构融合处理器上不同策略的自适应模型, 能够有进一步的性能提升.Ilgner等人[55]设计了异构融合处理器上的有限差分时域算法, 能够利用异构融合处理器的共享内存特性对算法进行加速.Liu等人设计了异构融合处理器上可以高效执行的稀疏矩阵-稀疏矩阵乘算法[61, 72]、稀疏矩阵向量乘算法[60], 并针对异构融合处理器的特性设计了堆数据结构[57].Zou等人[63]在异构融合处理器上实现了Smith-Waterman算法, 为了充分利用各设备, 设计了动态负载划分策略.Freytag等人[64]在异构融合处理器上研究非均匀域分解, 利用共享内存特性避免了设备间数据传输开销.

5.3 其他领域目前, 有研究工作使用GPU等异构设备加速网络应用中的数据包处理, 对于其中一些计算密集型的算法, GPU比CPU处理能力强; 然而, 由于CPU和离散GPU间的PCIe传输, GPU的加速效果大打折扣.为了避免不同设备间因数据传输所带来的时间开销, Go等人[65]设计了利用异构融合处理器进行加速的网络数据包处理器APUNet, 能够对诸多网络应用实现高效网络数据包处理.APUNet在所有阶段均可避免CPU和GPU间的数据传输, 更好地利用带宽, 释放GPU性能; 为了完成CPU和GPU间的低延迟通信, APUNet使多个GPU线程并行处理输入数据包流.Chang等人[66]基于异构融合处理器共享内存和低功耗等特性, 在异构融合处理器上探究了网络数据包分类应用.

对于机器学习领域, Gu等人[45]探索了在异构融合处理器上实现了深度神经网络模型, 并和离散GPU进行了比较.实验表明:异构融合处理器具有更高的性能功耗比, 在未来可搭建低功耗的深度神经网络计算平台.此外, 在视频处理领域, Zhu等人[67]在异构融合处理器上实现了高效帧频转换算法.

5.4 小结尽管异构融合处理器目前处于起步阶段, 在性能方面和高端GPU等加速器存在差距, 但异构融合处理器的出现使不同领域的研究人员看到了新的机会, 同时也被用在越来越多的领域中.例如在网络领域, 处理延迟至关重要, 而异构融合处理器中的GPU等设备能够直接高效对内存数据进行操作, 相对离散GPU具有一定优势.这些研究工作表明:异构融合处理器具有强劲的应用潜力, 在未来会有更多的展现机会.

6 异构融合处理器研究未来发展展望结合异构融合处理器不断演变的发展历程, 未来的异构融合处理器会集成更多的计算核心, 性能也会有进一步提升, 甚至可以应用于高性能服务器中.本节从新型体系结构研究、数据密集型研究、计算密集型研究等方面展望异构融合处理器的未来发展.

6.1 新型体系结构研究高性能计算指利用超级计算和并行处理技术解决复杂的计算问题.高性能计算技术通常设计并行处理算法和系统, 利用计算机仿真、计算机模拟和分析解决科学计算问题, 应用的领域包括生命科学、地理信息数据处理、石油勘探模拟、电力系统设计、气象模拟等方面.高性能计算涉及的这些问题关乎人们的日常生活, 然而, 解决更大、更复杂的问题也需要更强大的计算能力.特别是在大数据时代, 需要处理的数据量过于庞大, 设计新型的E级超级计算机(exaflops)来缓解新的技术需求变得越来越迫切.但由于计算机扩展性方面的限制, 简单将计算设备进行堆叠受限于功耗、内存和网络带宽, 来自数据传输等方面的开销过大, 难以达到所需要的计算能力.

异构融合处理器具有将传统处理器与加速设备相融合的特点, 可以从多方面满足设计E级超级计算机的需求:第一, 将高吞吐率设备如GPU等和CPU处理器相结合的设计可以兼顾不同类型的计算任务需求, 提高高性能计算机处理器的计算适应性; 第二, 异构融合处理器中的不同设备集成在一起可以共享相同的内存和存储设备, 紧密结合的设计可以避免加速设备和处理器分离所带来的数据传输开销, 扩展性更好; 第三, 不同类型处理器集成到一个芯片的设计可以采用更高效的功耗控制技术, 同时也可拥有更多的组件优化设计, 降低功耗和成本; 第四, 异构融合处理器可设计多级存储体系结构, 分层的存储设计可更充分地发挥异构融合处理器中不同设备的计算特性.目前的异构融合处理器仍处于发展阶段, 性能较弱.但如表 1所示, 有越来越多的研究者利用异构融合处理器解决科学计算相关的一系列计算任务, 和相同价位的GPU等异构计算设备相比, 异构融合处理器表现出了较强的计算能力和性能功耗比.同时, 尽管异构融合处理带来了诸多好处, 但集成芯片设计复杂, 同时各设备类型不同, 如果没有对不同的处理器有针对性地进行优化, 则可能出现较大的性能降级.如何设计高效的不同设备间的缓存一致性, 也是一个所面临的挑战.未来的高性能异构融合处理器设计需要考虑这些问题, 设计出性能更强的新型处理器.

编程语言是一种形式化语言, 包含了一组用于产生各种输出的计算机指令集.随着计算机体系结构的不断发展, 相应的编程语言也在不断发展、进化.从最原始的机器语言发展至现代的编程语言, 从可编程性、程序开发效率、维护效率等方面无不发生着巨大的变化.异构融合处理器的出现, 进一步加剧了能够适应新型处理设备的编程语言的需求.目前的研究表明:需要针对不同设备进行程序优化, 才能使异构融合处理器达到较优的性能, 需要在编写程序时充分了解体系结构特性, 对编程人员要求较高.未来的异构融合处理器可能会集成更多种类的设备, 包含多层异构存储体系结构, 并提供动态能耗弹性管理特性, 编程所需考虑的情况会更多样化, 这些考虑因素可能会令程序员无法专注于应用本身, 无法高效地开发程序.设计可编程性高、性能强的编程语言, 需要对硬件特性和编程模型进行充分探索, 对底层硬件从软件开发人员角度进行抽象, 运行时能够利用异构融合处理器的各种特性.

目前, 异构融合处理器最具代表性的编程语言是OpenCL, 被各大处理器生产厂商所支持.然而, 对于类似GPU等处理单元, 需要编程人员在代码中显式写明各线程如何并行处理数据、如何利用共享缓存, 以充分利用处理器资源, 而对于CPU处理器则不需要考虑这些操作.未来针对异构融合处理器的编程语言, 需要降低不同处理单元间的差异性以降低编程要求, 但同时应保证程序编译后仍具有较高的性能, 这要求编译器能够自动针对不同设备进行优化.例如, 对于一个循环操作, 编译器和运行时库能够自动为CPU和异构单元(如GPU)分配合适的循环并执行相关优化操作.与此同时, 由于开发通用目的编程语言(general-purpose language)充满挑战, 未来会出现越来越多的针对特定领域的编程语言(domain specific language), 能够针对某些领域提供特定程序接口, 高效利用异构融合处理器, 满足不同领域编程人员的开发需求.此外, 未来的编程语言设计还需配套相关编程辅助工具.具体包括:(1)简单、易于使用的代码调试工具, 能够对运行在异构融合处理器上的程序进行代码调试; (2)针对异构融合处理器的代码分析工具, 能够在可接受的时间范围内分析出程序的性能瓶颈位置以及计算、访存情况等信息; (3)自动调优工具, 能够辅助编程人员针对异构融合处理器优化数据存放位置、数据访问方式、计算模式等.

6.2 数据密集型应用研究以大数据为代表的数据密集型应用, 未来会在异构融合处理器的研究中扮演重要的角色.大数据指无法在一定时间内通过常规数据处理工具进行处理的大规模数据集合, 因为数据量过大, 传统的数据处理技术无法直接进行处理[73].大数据所带来的挑战不仅是数据存储, 还包括分析、搜索、传输、查询、更新、可视化等一系列挑战.大数据处理技术受益于计算机体系结构的发展, 各类计算处理单元为大数据系统提供底层支持, 在新型计算设备之上设计合适的数据结构和算法, 可以搭建出性能更强的大数据处理系统.近些年, 随着以GPU为代表的异构计算的兴起, 越来越多的大数据处理系统利用异构计算技术应对挑战.相对于CPU、GPU拥有更多的计算核心, 即更高的并行度.然而, 使用异构加速器件也存在着一些问题和挑战, 例如, 利用GPU等异构设备需要首先从CPU端传输数据, 存在时间开销; 其次, 异构设备通常使用独立的内存, 容量有限, 在大数据环境下难以一次性将全部数据装入设备内存; 再次, 对于图数据库等新型数据密集型应用[74, 75], 由于应用数据访问的不规则性, GPU等异构设备无法充分发挥其内在性能.而未来大数据处理对异构融合处理器的使用则可以解决这些问题, 多种异构设备集成到一个芯片集成了不同设备的特性, 并可以共享相同的物理内存, 避免了不同设备间的数据传输开销, 可以更高效地对大数据进行处理.

大数据处理等数据密集型应用, 使用异构融合处理器高效处理数据, 需要面对一系列新的挑战:第一, 异构融合处理器集成了多种设备, 对于大数据计算任务, 如何向不同的设备进行任务分配?是否需要在大数据处理系统内部设计不同处理器的调度策略?第二, 多种设备相集成的特性使得不同设备共享有限的内存带宽, 对于数据密集型应用, 如何设计数据处理策略, 使不同设备的数据处理过程不互相干扰, 也是一个亟待解决的挑战; 第三, 针对异构融合处理器的数据结构和大数据处理算法, 充分发挥新型硬件的计算能力, 以往适合传统处理器的数据结构和并行算法可能不适用于多设备融合的特点, 因此需要考虑不同设备差异进行设计; 第四, 大数据处理系统的操作人员可能不是计算机从业者, 有可能是统计等领域的从业人员, 如何保证异构融合处理器在大数据处理技术中的易用性, 也是一个需要面对的挑战.

6.3 计算密集型应用研究传统的高性能计算领域中, 计算密集型应用可受益于异构融合处理器的发展; 此外, 在计算机领域, 异构融合处理器有可能成为其中机器学习任务中计算密集型应用的新突破口.人工智能利用计算机程序实现人类智能技术, 而机器学习作为实现人工智能的一种方法, 大量使用GPU等异构加速设备.特别是对于深度学习中的深度神经网络训练, GPU等高并发加速设备使其能够在较短时间内完成训练.然而, 目前机器学习领域对异构设备的使用仍处于探索阶段, 存在诸多挑战:首先, 为了进一步提高训练模型的准确性, 灵活应对复杂的机器学习任务和应用场景, 需要用高维模型海量数据进行训练, 而目前流行的GPU等异构设备中有限的内存无法一次性装入大量数据, 需要数据和参数的传入、传出, 这会带来开销; 其次, GPU等加速设备往往对于规则的密集型计算任务较为适合, 而大规模机器学习中有可能遇到非规则计算型任务, 例如有可能会遇到稀疏特征等问题, GPU等加速效果有限, 需要进一步采取优化操作; 再次, 当涉及多个设备混合运算时, 每个设备都有独立的内存架构, 当需要跨设备进行数据访问时开销较大, 且当数据同时存在不同设备时, 较难维护数据的一致性.而异构融合处理器将不同加速设备相融合的特性, 为机器学习等人工智能领域应用加速带来了新的机遇.

机器学习应用与异构融合处理器相结合, 有如下考虑因素.

● 第一, 对于同样的机器学习应用, 可能存在多种机器学习训练模型结合不同的算法, 且模型间计算模式、数据依赖、访存模式等均不相同, 因此需要对机器学习模型和不同计算设备体系结构具有充分了解才能开发出针对异构融合处理器合适的模型.

● 第二, 面对大规模机器学习任务, 如何设计合理的数据结构, 充分考虑设备间体系结构差异, 提供高维模型海量数据的训练能力.

● 第三, 针对异构融合处理器机器学习系统的易用性和高效性等考虑因素, 需要为用户提供统一的编程接口; 同时, 机器学习系统内部能够充分考虑设备间的结构差异以及异构融合处理器的特性.

总之, 机器学习技术是目前学术界和工业界的研究热点, 对于异构融合处理器, 生产厂商也在不断尝试如何设计体系结构能够更贴合机器学习应用特性.相信在不远的将来, 可以看到异构融合处理器与机器学习技术相结合的新突破.

7 总结异构融合处理器将不同的设备集成到一个芯片, 为科学计算、大数据处理等领域带来了新的研究机会.但由于其共享内存、编程时需要考虑不同设备体系结构差异等特点, 异构融合处理器的研究与发展也存在不小的挑战.本文从异构融合处理器的性能分析、优化以及具体应用等角度, 对以往研究工作进行了分类与总结, 使用异构融合处理器编程需要充分考虑不同设备硬件特性、异构融合处理器特有特征以及负载特点; 在程序优化方面, 现有研究从性能和功耗角度对异构融合处理器进行了探索, 考虑了不同设备的特点与优化方式.同时, 异构融合处理器正被用于越来越广泛的领域, 这可为进一步的处理器设计提供参考.最后, 本文从高性能计算、编程模型、大数据处理、机器学习这4个方面对异构融合处理器的未来发展趋势进行了展望.

| [1] |

Foley D, Steinman M, Branover A, Smaus G, Asaro A, Punyamurtula S, Bajic L. AMD's 'Llano' fusion APU. In:Proc. of the Hot Chips, Vol.23., 2011, 1-38.

http://www.hotchips.org/wp-content/uploads/hc_archives/hc23/HC23.19.9-Desktop-CPUs/HC23.19.930-Llano-Fusion-Foley-AMD.pdf |

| [2] | |

| [3] |

Nikolskiy VP, Stegailov VV, Vecher VS. Efficiency of the Tegra K1 and X1 systems-on-chip for classical molecular dynamics. In:Proc. of the 2016 Int'l Conf. on High Performance Computing & Simulation (HPCS).Innsbruck, 2016, 682-689.

https://www.researchgate.net/publication/308189519_Efficiency_of_the_Tegra_K1_and_X1_systems-on-chip_for_classical_molecular_dynamics |

| [4] |

Vijayaraghavany T, Eckert Y, Loh GH, et al. Design and analysis of an APU for exascale computing. In:Proc. of the 2017 IEEE Int'l Symp. on High Performance Computer Architecture (HPCA).IEEE, 2017, 85-96.

https://www.researchgate.net/publication/316899937_Design_and_Analysis_of_an_APU_for_Exascale_Computing |

| [5] |

Schulte MJ, Ignatowski M, Loh GH, et al. Achieving exascale capabilities through heterogeneous computing. IEEE Micro, 2015, 35(4): 26-36.

[doi:10.1109/MM.2015.71] |

| [6] |

Colangelo P, Luebbers E, Huang R, et al. Application of convolutional neural networks on Intel Xeon processor with integrated FPGA. In:Proc. of the 2017 IEEE High Performance Extreme Computing Conf. (HPEC). IEEE, 2017, 1-7.

https://www.researchgate.net/publication/319066840_Application_of_Convolutional_Neural_Networks_on_Intel_R_Xeon_R_Processor_with_Integrated_FPGA |

| [7] |

Zhang F. Research on workload analysis and optimizations on heterogeneous integrated architectures[Ph.D. Thesis]. Beijing: Tsinghua University, 2017.

|

| [8] |

Zhang F, Zhai J, Chen W, He B, Zhang S. To co-run, or not to co-run:A performance study on integrated architectures. In:Proc. of the 2015 IEEE 23rd Int'l Symp. on Modeling, Analysis and Simulation of Computer and Telecommunication Systems (MASCOTS).IEEE, 2015, 89-92.

https://dl.acm.org/doi/10.1109/MASCOTS.2015.27 |

| [9] |

Zhu Q, Wu B, Shen X, Shen L, Wang Z. Understanding co-run degradations on integrated heterogeneous processors. In:Proc. of the Int'l Workshop on Languages and Compilers for Parallel Computing.Cham:Springer-Verlag, 2014, 82-97.

https://link.springer.com/chapter/10.1007/978-3-319-17473-0_6 |

| [10] |

Zhu Q, Wu B, Shen X, Shen K, Shen L, Wang Z. Understanding co-run performance on CPU-GPU integrated processors:Observations, insights, directions. Frontiers of Computer Science, 2017, 11(1): 130-146.

[doi:10.1007/s11704-016-5468-8] |

| [11] |

Zhang F, Zhai J, He B, Zhang S, Chen W. Understanding co-running behaviors on integrated CPU/GPU architectures. IEEE Trans. on Parallel and Distributed Systems, 2017, 28(3): 905-918.

[doi:10.1109/TPDS.2016.2586074] |

| [12] |

Pandit P, Govindarajan R. Fluidic kernels:Cooperative execution of OpenCL programs on multiple heterogeneous devices. In:Proc. of the Annual IEEE/ACM Int'l Symp. on Code Generation and Optimization.ACM, 2014.

https://www.researchgate.net/publication/261857147_Fluidic_Kernels_Cooperative_Execution_of_OpenCL_Programs_on_Multiple_Heterogeneous_Devices |

| [13] |

Stone JE, Gohara D, Shi G. OpenCL:A parallel programming standard for heterogeneous computing systems. Computing in Science & Engineering, 2010, 12(3): 66-73.

https://www.ncbi.nlm.nih.gov/pmc/articles/PMC2964860/ |

| [14] |

Zhu Q, Wu B, Shen X, Shen L, Wang Z. Co-run scheduling with power cap on integrated CPU-GPU systems. In:Proc. of the 2017 IEEE Int'l Parallel and Distributed Processing Symp. (IPDPS).IEEE, 2017, 967-977.

https://www.researchgate.net/publication/318125399_Co-Run_Scheduling_with_Power_Cap_on_Integrated_CPU-GPU_Systems |

| [15] |

Garzón EM, Moreno JJ, Martínez JA. An approach to optimise the energy efficiency of iterative computation on integrated GPU-CPU systems. The Journal of Supercomputing, 2017, 73(1): 114-125.

http://www.wanfangdata.com.cn/details/detail.do?_type=perio&id=23d72692e1f4380b8a711c1366d5962a |

| [16] |

Sanders J, Kandrot E. CUDA by Example:An Introduction to General-purpose GPU Programming. Addison-Wesley Professiona, 2010.

|

| [17] |

Krishnan G, Bouvier D, Naffziger S. Energy-efficient graphics and multimedia in 28-nm Carrizo accelerated processing unit. IEEE Micro, 2016, 36(2): 22-33.

[doi:10.1109/MM.2016.24] |

| [18] |

Doweck J, Kao WF, Lu AKY, et al. Inside 6th-generation Intel core:New microarchitecture code-named Skylake. IEEE Micro, 2017, 37(2): 52-62.

[doi:10.1109/MM.2017.38] |

| [19] |

Boggs D, Brown G, Tuck N, Venkatraman KS. Denver:Nvidia's first 64-bit ARM processor. IEEE Micro, 2015, 35(2): 46-55.

[doi:10.1109/MM.2015.12] |

| [20] |

Lee K, Lin H, Feng WC. Performance characterization of data-intensive kernels on AMD fusion architectures. Computer Science-Research and Development, 2013, 28(2-3): 175-184.

[doi:10.1007/s00450-012-0209-1] |

| [21] |

Dashti M, Fedorova A. Analyzing memory management methods on integrated CPU-GPU systems. ACM SIGPLAN Notices, 2017, 52(9): 59-69.

[doi:10.1145/3156685.3092256] |

| [22] |

Yang Y, Xiang P, Mantor M, Zhou H. CPU-assisted GPGPU on fused CPU-GPU architectures. In:Proc. of the 2012 IEEE 18th Int'l Symp. on High Performance Computer Architecture (HPCA)

IEEE, 2012, 1-12.

https://www.researchgate.net/publication/254021753_CPU-assisted_GPGPU_on_fused_CPU-GPU_architectures |

| [23] |

Power J, Basu A, Gu J, Puthoor S, Beckmann BM, Hill MD, Reinhardt SK, Wood DA. Heterogeneous system coherence for integrated CPU-GPU systems. In:Proc. of the 46th Annual IEEE/ACM Int'l Symp. on Microarchitecture.ACM, 2013, 457-467.

https://www.researchgate.net/publication/262404600_Heterogeneous_system_coherence_for_integrated_CPU-GPU_systems |

| [24] |

Agarwal N, Nellans D, Ebrahimi E, Wenisch TF, Danskin J, Keckler SW. Selective GPU caches to eliminate CPU-GPU HW cache coherence. In:Proc. of the 2016 IEEE Int'l Symp. on High Performance Computer Architecture (HPCA).IEEE, 2016, 494-506.

https://www.researchgate.net/publication/299641327_Selective_GPU_caches_to_eliminate_CPU-GPU_HW_cache_coherence |

| [25] |

Choi YK, Cong J, Fang Z, Hao Y, Reinman G, Wei P. A quantitative analysis on microarchitectures of modern CPU-FPGA platforms. In:Proc. of the 53rd Annual Design Automation Conf.ACM, 2016.

https://dl.acm.org/doi/10.1145/2897937.2897972 |

| [26] |

Cong J, Fang Z, Huang M, Wang L, Wu D. CPU-FPGA co-scheduling for big data applications. IEEE Design & Test, 2018, 35(1): 16-22.

http://www.sfu.ca/~zhenman/files/J2-DT2018-CPU-FPGA-Coschedule.pdf |

| [27] |

Nichols B, Buttlar D, Farrell J. Pthreads Programming:A POSIX Standard for Better Multiprocessing. O'Reilly Media, Inc., 1996.

https://works.bepress.com/besqoorarma/30/ |

| [29] |

Daga M, Aji AM, Feng WC. On the efficacy of a fused CPU+ GPU processor (or APU) for parallel computing. In:Proc. of the 2011 Symp. on Application Accelerators in High-performance Computing (SAAHPC).IEEE, 2011, 141-149.

https://www.researchgate.net/publication/224259813_On_the_efficacy_of_a_fused_CPUGPU_processor_or_APU_for_parallel_computing |

| [30] |

Spafford KL, Meredith JS, Lee S, Li D, Roth PC, Vetter JS. The tradeoffs of fused memory hierarchies in heterogeneous computing architectures. In:Proc. of the 9th Conf. on Computing Frontiers.ACM, 2012, 103-112.

https://www.researchgate.net/publication/254005059_The_tradeoffs_of_fused_memory_hierarchies_in_heterogeneous_computing_architectures |

| [31] |

Zakharenko V, Aamodt T, Moshovos A. Characterizing the performance benefits of fused CPU/GPU systems using FusionSim. In:Proc. of the Design, Automation & Test in Europe Conf. & Exhibition (DATE).IEEE, 2013, 685-688.

https://dl.acm.org/doi/10.5555/2485288.2485455 |

| [32] |

Zhang F, Wu B, Zhai J, He B, Chen W. FinePar:Irregularity-aware fine-grained workload partitioning on integrated architectures. In:Proc. of the 2017 IEEE/ACM Int'l Symp. on Code Generation and Optimization (CGO).IEEE, 2017, 27-38.

https://xueshu.baidu.com/usercenter/paper/show?paperid=f40f094fd720d88a4fa85a78bcdce5a6&site=xueshu_se&hitarticle=1 |

| [33] |

Zhang F, Liu W, Feng N, et al. Performance evaluation and analysis of sparse matrix and graph kernels on heterogeneous processors. CCF Trans. on High Performance Computing, 2019, 1(2): 131-143.

[doi:10.1007/s42514-019-00008-6] |

| [34] |

Mekkat V, Holey A, Yew PC, Zhai A. Managing shared last-level cache in a heterogeneous multicore processor. In:Proc. of the 22nd Int'l Conf. on Parallel Architectures and Compilation Techniques.IEEE, 2013, 225-234.

http://doi.ieeecomputersociety.org/10.1109/PACT.2013.6618812 |

| [35] |

Said I, Fortin P, Lamotte JL, et al. Leveraging the accelerated processing units for seismic imaging:A performance and power efficiency comparison against CPUs and GPUs. The Int'l Journal of High Performance Computing Applications, 2018, 32(6): 819-837.

[doi:10.1177/1094342017696562] |

| [36] |

Dávila GP, Oliveira D, Navaux P, et al. Impact of workload distribution on energy consumption, performance, and reliability of heterogeneous devices. In:Proc. of the 201927th Euromicro Int'l Conf. on Parallel, Distributed and Network-based Processing (PDP).IEEE, 2019, 166-173.

https://www.researchgate.net/publication/331953664_Impact_of_Workload_Distribution_on_Energy_Consumption_Performance_and_Reliability_of_Heterogeneous_Devices |

| [37] | |

| [38] |

Barik R, Kaleem R, Majeti D, Lewis BT, Shpeisman T, Hu C, Ni Y, Adl-Tabatabai AR. Efficient mapping of irregular C++ applications to integrated GPUs. In:Proc. of the Annual IEEE/ACM Int'l Symp. on Code Generation and Optimization.ACM, 2014.

https://www.researchgate.net/publication/262163399_Efficient_Mapping_of_Irregular_C_Applications_to_Integrated_GPUs |

| [39] |

Kaleem R, Barik R, Shpeisman T, Lewis BT, Hu C, Pingali K. Adaptive heterogeneous scheduling for integrated GPUs. In:Proc. of the 23rd Int'l Conf. on Parallel Architectures and Compilation.ACM, 2014, 151-162.

https://www.researchgate.net/publication/263083270_Adaptive_heterogeneous_scheduling_for_integrated_GPUs |

| [40] |

Tang S, He B, Zhang S, Niu Z. Elastic multi-resource fairness:balancing fairness and efficiency in coupled CPU-GPU architectures. In:Proc. of the Int'l Conf. for High Performance Computing, Networking, Storage and Analysis.IEEE, 2016.

https://ieeexplore.ieee.org/document/7877153 |

| [41] |

Puthoor S, Aji AM, Che S, Daga M, Wu W, Beckmann BM, Rodgers G. Implementing directed acyclic graphs with the heterogeneous system architecture. In:Proc. of the 9th Annual Workshop on General Purpose Processing using Graphics Processing Unit.ACM, 2016, 53-62.

https://dl.acm.org/doi/10.1145/2884045.2884052 |

| [42] |

Cho Y, Negele F, Park S, Egger B, Gross TR. On-the-fly workload partitioning for integrated CPU/GPU architectures. In:Proc. of the 27th Int'l Conf. on Parallel Architectures and Compilation Techniques.ACM, 2018.

|

| [43] |

Zhang F, Zhai J, Wu B, et al. Automatic irregularity-aware fine-grained workload partitioning on integrated architectures. IEEE Trans. on Knowledge and Data Engineering, 2019.

[doi:10.1109/TKDE.2019.2940184]https://ieeexplore.ieee.org/abstract/document/8827952] |

| [44] |

Bouvier D, Sander B. Applying AMDs Kaveri APU for heterogeneous computing. In:Proc. of the Hot Chips:A Symp. on High Performance Chips (HC26)., 2014.

https://dblp.uni-trier.de/rec/conf/hotchips/BouvierS14 |

| [45] |

Gu J, Zhu M, Zhou Z, Zhang F, Lin Z, Zhang Q, Breternitz M. Implementation and evaluation of deep neural networks (DNN) on mainstream heterogeneous systems. In:Proc. of the 5th Asia-Pacific Workshop on Systems.ACM, 2014.

https://dl.acm.org/doi/10.1145/2637166.2637229 |

| [46] |

Hetherington TH, Rogers TG, Hsu L, O'Connor M, Aamodt TM. Characterizing and evaluating a key-value store application on heterogeneous CPU-GPU systems. In:Proc. of the 2012 IEEE Int'l Symp. on Performance Analysis of Systems and Software (ISPASS).IEEE, 2012, 88-98.

https://www.researchgate.net/publication/254029356_Characterizing_and_evaluating_a_key-value_store_application_on_heterogeneous_CPU-GPU_systems |

| [47] |

Daga M, Nutter M. Exploiting coarse-grained parallelism in B+ tree searches on an APU. In:Proc. of the 2012 SC Companion High Performance Computing, Networking, Storage and Analysis (SCC).IEEE, 2012, 240-247.

https://ieeexplore.ieee.org/document/6495822 |

| [48] |

Chen L, Huo X, Agrawal G. Accelerating MapReduce on a coupled CPU-GPU architecture. In:Proc. of the Int'l Conf. on High Performance Computing, Networking, Storage and Analysis.IEEE Computer Society Press, 2012.

|

| [49] |

He J, Lu M, He B. Revisiting co-processing for Hash joins on the coupled CPU-GPU architecture. Proc. of the VLDB Endowment, 2013, 6(10): 889-900.

[doi:10.14778/2536206.2536216] |

| [50] |

He J, Zhang S, He B. In-cache query co-processing on coupled CPU-GPU architectures. Proc. of the VLDB Endowment, 2014, 8(4): 329-340.

[doi:10.14778/2735496.2735497] |

| [51] |

Kim S, Bottleson J, Jin J, Bindu P, Sakhare SC, Spisak JS. Power efficient MapReduce workload acceleration using integrated-GPU. In:Proc. of the 2015 IEEE 1st Int'l Conf. on Big Data Computing Service and Applications (Big Data Service)IEEE, 2015, 162-169.

https://dl.acm.org/doi/10.1109/BigDataService.2015.12 |

| [52] |

Zhang K, Hu J, He B, Hua B. Dido:Dynamic pipelines for in-memory key-value stores on coupled CPU-GPU architectures. In:Proc. of the 2017 IEEE 33rd Int'l Conf. on Data Engineering (ICDE).IEEE, 2017, 671-682.

https://ieeexplore.ieee.org/document/7930016 |

| [53] |

Zhang F, Yang L, Zhang S, et al. FineStream:Fine-grained window-based stream processing on CPU-GPU integrated architectures. In:Proc. of the USENIX Annual Technical Conf.(USENIX ATC), 2020.

|

| [54] |

Doerksen M, Solomon S, Thulasiraman P. Designing APU oriented scientific computing applications in OpenCL. In:Proc. of the 2011 IEEE 13th Int'l Conf. on High Performance Computing and Communications (HPCC).IEEE, 2011, 587-592.

https://ieeexplore.ieee.org/document/6063044 |

| [55] |

Ilgner RG, Davidson DB. A comparison of the FDTD algorithm implemented on an integrated GPU versus a GPU configured as a co-processor. In:Proc. of the 2012 Int'l Conf. on Electromagnetics in Advanced Applications (ICEAA).IEEE, 2012, 1046-1049.

https://ieeexplore.ieee.org/document/6328782 |

| [56] |

Delorme MC, Abdelrahman TS, Zhao C. Parallel radix sort on the AMD fusion accelerated processing unit. In:Proc. of the 201342nd Int'l Conf. on Parallel Processing (ICPP).IEEE, 2013, 339-348.

https://ieeexplore.ieee.org/document/6687367 |

| [57] |

Liu WF, Vinter B. Ad-Heap:An efficient heap data structure for asymmetric multicore processors. In:Proc. of the Workshop on General Purpose Processing Using GPUs.ACM, 2014.

|

| [58] |

Daga M, Nutter M, Meswani M. Efficient breadth-first search on a heterogeneous processor. In:Proc. of the 2014 IEEE Int'l Conf. on Big Data (Big Data).IEEE, 2014, 373-382.

https://ieeexplore.ieee.org/document/7004254 |

| [59] |

Eberhart P, Said I, Fortin P, Calandra H. Hybrid strategy for stencil computations on the APU.In:Proc. of the 1st Int'l Workshop on High-performance Stencil Computations. Vienna, 2014, 43-49.

|

| [60] |

Liu WF, Vinter B. Speculative segmented sum for sparse matrix-vector multiplication on heterogeneous processors. Parallel Computing, 2015, 49: 179-193.

[doi:10.1016/j.parco.2015.04.004] |

| [61] |

Liu W, Vinter B. A framework for general sparse matrix-matrix multiplication on GPUs and heterogeneous processors. Journal of Parallel and Distributed Computing, 2015, 85: 47-61.

[doi:10.1016/j.jpdc.2015.06.010] |

| [62] |

Zhang F, Lin H, Zhai J, et al. An adaptive breadth-first search algorithm on integrated architectures. The Journal of Supercomputing, 2018, 74(11): 6135-6155.

[doi:10.1007/s11227-018-2525-0] |

| [63] |

Zou H, Tang S, Yu C, et al. ASW:Accelerating Smith-Waterman algorithm on coupled CPU-GPU architecture. Int'l Journal of Parallel Programming, 2019, 47(3): 388-402.

[doi:10.1007/s10766-018-0617-3] |

| [64] |

Freytag G, Navaux POA, Lima JVF, et al. Non-uniform domain decomposition for heterogeneous accelerated processing units. In:Proc. of the Int'l Conf. on Vector and Parallel Processing.Cham:Springer, 2018, 105-118.

https://link.springer.com/chapter/10.1007/978-3-030-15996-2_8 |

| [65] |

Go Y, Jamshed MA, Moon Y, Hwang C, Park K. APUNet:Revitalizing GPU as packet processing accelerator. In:Proc. of the NSDI., 2017, 83-96.

|

| [66] |

Chang YK, Chi TY. Hash-based OpenFlow packet classification on heterogeneous system architecture.In:Proc. of the 201911th Int'l Conf. on Ubiquitous and Future Networks (ICUFN). IEEE, 2019, 300-305.

|

| [67] |

Zhu H, Wang D, Zhang P, et al. Parallel implementations of frame rate up-conversion algorithm using OpenCL on heterogeneous computing devices. Multimedia Tools and Applications, 2019, 78(7): 9311-9334.

[doi:10.1007/s11042-018-6532-1] |

| [68] |

Che S, Boyer M, Meng J, Tarjan D, Sheaffer JW, Lee SH, Skadron K. Rodinia:A benchmark suite for heterogeneous computing. In:Proc. of the IEEE Int'l Symp. on Workload Characterization (IISWC 2009).IEEE, 2009, 44-54.

https://ieeexplore.ieee.org/document/5306797 |

| [69] | |

| [70] |

Dean J, Ghemawat S. MapReduce:Simplified data processing on large clusters. Communications of the ACM, 2008, 51(1): 107-113.

[doi:10.1145/1327452.1327492] |

| [71] | |

| [72] |

Liu WF, Vinter B. An efficient GPU general sparse matrix-matrix multiplication for irregular data. In:Proc. of the 2014 IEEE 28th Int'l Parallel and Distributed Processing Symp.IEEE, 2014, 370-381.

https://ieeexplore.ieee.org/document/6877271 |

| [73] |

Pan W, Li Z, Zhang Y, et al. The new hardware development trend and the challenges in data management and analysis. Data Science and Engineering, 2018, 3(3): 263-276.

[doi:10.1007/s41019-018-0072-6] |

| [74] |

Lin XM, Yu JX. Special issue on graph processing:Techniques and applications. Data Science and Engineering, 2017, 2: 1.

[doi:10.1007/s41019-017-0036-2] |

| [75] |

Cheng Y, Ding P, Wang T, et al. Which category is better:Benchmarking relational and graph database management systems. Data Science and Engineering, 2019, 4(4): 309-322.

[doi:10.1007/s41019-019-00110-3] |

| [7] |

张峰. 面向集成异构平台的负载分析与优化关键技术研究[博士学位论文]. 北京: 清华大学, 2017.

|

| [28] |

28Dagum L, Menon R. OpenMP:An industry standard API for shared-memory programming. IEEE Computational Science and Engineering, 1998, 5(1): 46-55.

https://www.researchgate.net/publication/3344403_OpenMP_an_industry_standard_API_for_shared-memory_programming |

2020, Vol. 31

2020, Vol. 31