2. 中国科学院大学, 北京 100049;

3. 计算机科学国家重点实验室(中国科学院 软件研究所), 北京 100190;

4. 国家并行计算机工程技术研究中心, 北京 100190;

5. 北京大学 数学科学学院, 北京 100871

2. University of Chinese Academy of Sciences, Beijing 100049, China;

3. State Key Laboratory of Computer Science(Institute of Software, The Chinese Academy of Sciences), Beijing 100190, China;

4. National Research Center of Parallel Computer Engineering and Technology, Beijing 100190, China;

5. School of Mathematical Sciences, Peking University, Beijing 100871, China

稀疏矩阵向量乘(SpMV) y=Ax是科学与工程计算中一个非常重要的计算内核, 其性能往往对应用整体性能有着很大影响.SpMV是属于访存密集型的, 算法中的浮点计算与存储访问的比率很低, 且稀疏矩阵非零元素分布很不规则, 使得向量x为间接访问且访问不规则, 可重用性差, 这些因素给SpMV的高效实现带来很大挑战.

目前, 超级计算机的体系结构已经从多核向众核乃至异构众核发展, 然而访存墙问题却越来越突出, 带宽受限型操作的峰值性能也越来越低, 并且实现难度逐步增大.由我国国家并行计算机工程技术研究中心研制的新一代申威异构众核处理器已经面世, 其峰值性能为3TFlops/s, 聚合访存带宽为130GB/s, 相比计算能力, 其访存能力偏弱, 给稀疏矩阵向量乘的高效实现带来了巨大的挑战.本文针对该处理器特点, 提出一种面向传统的稀疏矩阵存储格式CSR的通用SpMV异构众核并行算法, 并从任务划分、LDM空间划分、向量x访存优化、负载均衡、自适应优化等角度开展工作.

1 相关工作介绍SpMV的实现和优化, 一直是高性能计算领域科研人员的研究重点.每当一款新的处理器问世, 基于该处理器的SpMV实现及优化的工作就会持续出现.基于CPU的SpMV工作有很多, 主要从存储格式[1, 2]、分块算法[3-5]、值和索引压缩[6, 7]、向量化[8, 9]、自适应优化[10, 11]等角度开展研究.

2008年, GPGPU出现, 开启了GPU用于通用计算的热潮.随后, 基于GPU的SpMV工作大量涌现, 这些工作主要通过存储格式、重排、压缩、自适应调优等技术解决带宽利用率、负载均衡、并行度等问题, 先后提出了HYB[12], ELLPACK-R[13], sliced-ELLPACK[14], blocked ELLPACK[15], BRC[16], BCCOO[17]等新型存储格式; 研究了稀疏矩阵的重排技术[18]及压缩格式[19], 以减少访存开销; 研究了GPU平台体系结构特征、稀疏矩阵存储格式、稀疏矩阵集之间的关系, 并给出自动选择模型[20]; 另外还研究了自动调优技术[17, 21, 22], 以根据稀疏矩阵的特征选择最优参数并获取较优的性能.

2011年, Intel公司的异构众核处理器Xeon Phi发布.随后, Liu等人[23]提出了新的ESB格式, 该格式可有效改善Xeon Phi上SpMV向量化性能, 并能减少访存开销, 另外还提出了混合的动态调度器以改善并行任务的负载均衡性; Tang等人[24]通过新的存储格式VHCC、二维不规则任务划分、自动调优技术等优化了一类scale-free稀疏矩阵SpMV的性能.

另外还有一类工作涉及到多个异构众核处理器, Kreutzer等人[25]主要从改善向量化性能的角度提出新的存储格式SELL-C-σ; Liu等人[26]提出了CSR5存储格式用于改善不规则稀疏矩阵SpMV的性能, 在多个异构众核处理器上实现并与现有最优工作进行了对比.

本文主要研究面向申威26010异构众核处理器的SpMV并行算法及实现和优化技术, 以支撑该国产平台相关应用.

2 国产申威26010处理器介绍国产申威26010处理器采用异构众核架构, 由4个核组(core group, 简称CG)组成, 其双精度计算能力3TFlops/s, 单处理器拥有260个核心, 采用共享存储架构, 聚合访存带宽130GB/s.基于该处理器搭建了国产神威太湖之光超级计算机, 已经部署于国家超算无锡中心, 其峰值性能超过100PFlops/s.

本文主要在其一个核组上开展工作, 如图 1所示.每个核组由控制核心(management processing element, 简称MPE, 又称主核)、计算核心簇(computing processing elements clusters, 简称CPE cluster, 又称从核)、协议处理部件(PPU)和存储控制器(memory controller, 简称MC)组成.

|

Fig. 1 The architecture of SW26010 processor 图 1 国产申威26010处理器单核组架构图 |

平均每个核组的访存带宽为32.5GB/s, 实测带宽为27.5GB/s.

主核采用通用的RISC架构, 向量化宽度256位, 采用一级数据和指令Cache分离、二级指令数据共享的两级片上存储层次.从核核组采用拓扑为8×8 mesh互联, 包含64个计算核心和DMA(DMA controller)控制器.计算核心采用精简的64位RISC指令集, 向量化宽度为256位, 有64KB的Scratch Pad Memory(又称LDM), 通过DMA可实现内存与LDM间的快速数据传输.应用程序由控制核心启动, 借助高性能线程库Athread将计算任务异步加载到计算核心执行, 双方通过同步接口协同.

3 CSR格式简介CSR格式是目前稀疏矩阵使用最广泛的一种存储格式.设待存储的稀疏矩阵A是m×n维的, 有nz个非零元, 其通过3个一维数组来存储稀疏矩阵的信息, 具体如下:

● val[nz], 记录每个非零元的值;

● col[nz], 记录每个非零元所在的列;

● ptr[m+1], 记录每行的第1个非零元在数组val[nz]和col[nz]中的索引, 其中, ptr[m]=nz.

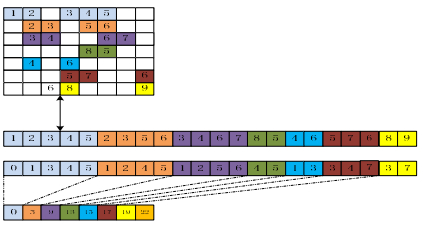

图 2给出了一个示例.目前, 大多数科学与工程计算应用的矩阵中均采用CSR格式进行存储, 国际上SpMV算法的研究也大都以CSR格式为基准, 如果采用其他存储格式, 还需衡量该格式到CSR格式的转换开销, 故本文直接研究基于CSR格式的SpMV算法.

|

Fig. 2 The CSR format 图 2 CSR格式示意图 |

4 SpMV异构众核并行算法 4.1 任务划分

申威众核处理器每个核组包括1个主核和64个从核, 为了充分利用从核核组的计算资源, 我们将计算任务尽可能的分给从核, 主核主要负责前处理和控制.

对于稀疏矩阵而言, 任务划分方法有两种:一维划分和二维划分.二维划分时, 多个从核会同时更新y向量的一部分, 需要加锁处理, 从而导致额外的开销.对规则稀疏矩阵而言, 每行的非零元个数较少, LDM可以容纳至少一行计算所需的元素, 所以我们采用一维的任务划分方法.如果矩阵一行的非零元太多, 导致LDM空间不能一次容纳一行的元素进行计算, 那么将采用主核进行计算.

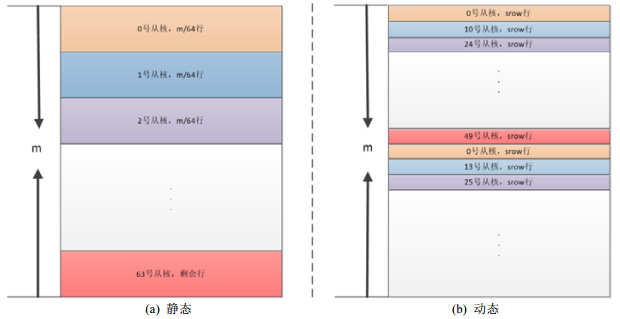

一维划分方式又有两种(如图 3所示, 其中, srow为当前申威处理器一个从核的LDM可以容纳的最多稀疏行大小).静态任务划分:将矩阵按行等分, 每个从核计算m/64行, 从核的内部循环开始执行, 每次只计算矩阵的srow行; 动态任务划分:将矩阵srow行的计算视为一个子任务, 形成任务池.每个从核一次只负责一个子任务, 执行结束后, 再取下一个子任务进行计算.

|

Fig. 3 Task partition 图 3 任务划分示意图 |

具体计算方式见第4.2节.静态任务划分方式每个从核执行的矩阵行数基本相同; 动态任务划分方式时, 每个从核执行的矩阵行数根据当前从核的执行情况动态调整, 总矩阵行数可能大不相同.这两种方式分别适用于不同类型的稀疏矩阵, 见第5.2节.

4.2 LDM空间划分每个从核的LDM空间相当于一块高速缓存, 从核访问LDM中的数据仅需要数拍即可完成, 而从核直接访问主存则需要200多拍, 所以LDM空间的使用对并行算法的设计至关重要.每个从核的LDM空间仅有64KB, 而CSR格式的SpMV计算需要val, col, ptr, x, y这5个数组的值才能完成.根据第4.1节中的任务划分方式, 每个从核每次只计算srow行, 那么y的空间只需srow大小, 其余行计算时可以重复利用此块空间; ptr数组类似, 只需srow+1大小.由于SpMV计算中x的访存是不连续且不规则的, 对整体性能影响很大.为此, 我们为其预留较多的空间以增加命中率.

每个从核64KB空间分配如下:24KB用于存储x, y, ptr和其他局部变量, 40KB用于存放val和col.由于val为双精度数据类型, col为整型数据类型, 共占12字节, 所以40KB空间最多只能存储40×1024/12个val和col元素, 即3 413个.那么srow=3413/maxnz, 其中, maxnz为该稀疏矩阵每行最大的非零元个数.若采用双缓冲优化, 则该值减半, val, col, ptr均设置两块buffer, 大小为原来的一半.

x设置2块buffer:一块静态buffer, 其大小为xssize; 一块动态buffer, 其大小为xdsize.静态buffer加载一次后重复使用; 动态buffer在静态buffer没有命中时使用, 如没有命中, 则从当前所需的x处加载xdsize个数据到动态buffer, 后续计算时先查找静态buffer, 再查找动态buffer, 如果没有命中, 继续加载xdsize个数据到动态buffer中.具体流程如图 4所示.

|

Fig. 4 The flowchart of dynamic and static buffer loading of x 图 4 x的动静态buffer加载示意图 |

对每个矩阵而言, xssize的最大值由srow确定, 该缓冲区的大小直接影响了SpMV的最终性能.对于xdsize的选择, 我们期望读取一次的开销与访问一次主存的开销相当.经测试, DMA传递32个元素的开销与访问一次主存的开销相当, 故xdsize设置为32.

5 实现及优化 5.1 x访存优化稀疏矩阵向量乘中, x是间接访存, 访存行为很不规则, 在申威众核处理器上, x的访存是优化的重点, 直接对其最终性能起到决定性的影响.x的访存有几种方式.

(1) 所有的x直接从主存读取;

(2) 每个从核通过DMA预取部分x, 其余x通过访问主存得到, 记为static-dma;

(3) 动静态buffer方式, 记为static-dynamic.具体见第4.2节.

由于从核访问一次主存约需200多拍, 方案1性能明显很差, 所以实际中并未使用.方案2和方案3中静态buffer的大小见第4.2节.第6.2.1节给出了两种方案的性能对比结果.

另外, 加载静态buffer的初始位置对SpMV的性能也有一些影响.初始位置有两种选择.

1) 从当前从核计算的行块的起始位置读取, 记为start-x-row;

2) 从当前从核计算行块所需的第一个x处读取, 记为start-x-current.

5.2 负载均衡稀疏矩阵每行的非零元个数不尽相同, 且分布不均.按照图 3(a)中的静态任务划分方法, 对有些矩阵会导致从核间负载不均衡, 这个负载不均衡来自两个方面.

● 每个从核计算的行块的总非零元个数可能差异较大;

● 每个从核计算的行块中x的访存行为可能差异较大.

为了解决负载不均衡的问题, 本文还采用了动态任务划分的方式, 如图 3(b)中所示.该方式中, 从核间协同, 通过采用我们自己用原子操作实现的锁来完成.

然而, 由于目前的锁实现中需要访问主存, 这个代价比较高, 所以其性能较差, 具体见第6.2.2节.

为此, 本文对这种调度方式进一步进行了优化, 只在第1次运行SpMV时采用动态调度, 并记录每个计算核心所分配的任务, 在以后的执行过程中, 均按照这种方式来进行任务分配, 我们将其称为动-静态任务调度.

5.3 自适应优化由于实际应用中稀疏矩阵千差万别, 非零元的分布方式各不相同.对每一个稀疏矩阵而言, 任务分配方式、静态buffer大小、静态buffer加载的起始位置等均对其性能有着很大的影响, 有必要针对该稀疏矩阵选择最优的参数组合.可选的参数如下:

● 调度方式, 有两种选择:静态调度和动静态结合的调度方式;

● 静态buffer读取的起始位置;

● 静态buffer的大小, 其最大值受LDM限制, 每个矩阵均不同, 初始值选为128, 每128递增.

为了减少搜索开销, 本文对Matrix Market矩阵集中57个不同类型的稀疏矩阵选择不同参数的性能结果进行分析, 发现任务调度方式、静态buffer读取的起始位置均与静态buffer的大小关系不大, 据此, 本文确定了如图 5的搜索顺序.

|

Fig. 5 The flowchart of search of optimal parameter 图 5 最优参数搜索顺序图 |

该搜索过程需要大约3~22个SpMV的时间, 但是对于实际应用来说, 这个过程可以预先进行, 以便于在以后的迭代过程中选用性能最高的SpMV实现.

5.4 双缓冲优化该处理器从核上支持DMA访存与计算重叠, 为了验证其有效性, 本文设置LDM上val, col, ptr的双buffer.图 6中, 上图展示了单buffer的计算和访存流程, 下图展示了双buffer的计算和访存流程.但该异构众核SpMV算法中主要以DMA操作为主, 计算所占的比重很小, 该优化对整体的性能影响不大.

|

Fig. 6 SpMV with CSR format in timeline 图 6 CSR格式SpMV时序图 |

6 实验结果 6.1 实验平台

我们采用神威“太湖之光”的一个核组作为测试平台, 借助高性能线程库Athread将计算任务异步加载到从核执行.测试矩阵选用了Matrix Market矩阵集中的矩阵进行测试, 矩阵规模从数千到百万, 矩阵非零元个数从数万到1 00多万.表 1中给出了测试矩阵的基本信息.

| Table 1 The information of test matrices 表 1 测试矩阵信息表 |

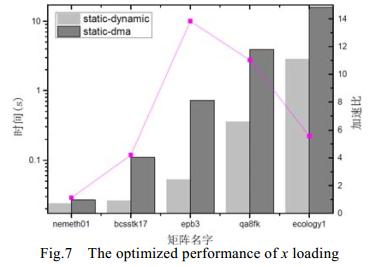

6.2 测试结果 6.2.1 x访存优化的对比结果

图 7中比较了第5.1节中提到的方案2和方案3的性能, 从图中可以看出, 方案3明显优于方案2, 最高加速比可达21倍.这是因为方案3利用了稀疏矩阵的局部性, 动态缓冲区的x数据得以重复利用.

|

Fig. 7 The optimized performance of x loading 图 7 x访存优化效果对比图 |

图 8中给出了部分矩阵选用两种加载静态buffer的起始位置的性能对比.矩阵qa8fk, raefsky2, cavity20选用方案2性能较好, 而cant和s3dkq4m2是选用方案1性能较好, 性能差最大的有55%, 最小的也有11%.

|

Fig. 8 The impact of the start position of loading dynamic/static buffer on performance 图 8 加载动静态buffer的初始位置对性能的影响 |

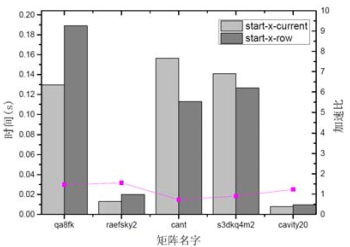

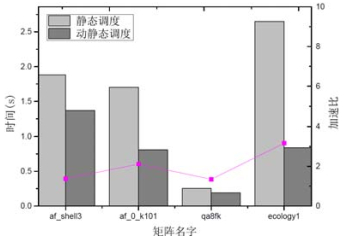

6.2.2 任务调度

由于稀疏矩阵千差万别, 不同的任务调度方式对其优化的效果也不尽相同, 图 9中给出了动-静态调度方式性能较好的测试矩阵的结果, 并将其与静态调度方式进行了对比.其中, 两种调度方式均采用从当前所需的第1个x作为起点加载静态buffer, 并且选用了xssize可选范围内的最优性能.从图中可以看出, 最大加速比可以达到6倍多, 说明不同任务调度方式对某些矩阵的性能有着很大的影响.

|

Fig. 9 The impact of different scheduling 图 9 不同的任务调度方式的优化效果 |

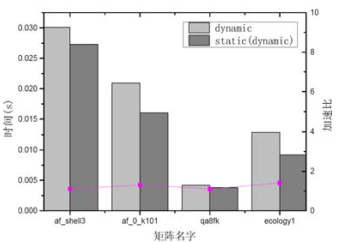

第6.2节中提到:动态调度时, 由于加锁引入了额外的开销.图 10中比较了采用动态调度进行计算的时间(记为dynamic)与利用动态调度的任务划分方式进行静态分配的计算时间(记为static(dynamic)), 其性能约有10%~ 40%的差异.

|

Fig. 10 Comparison of the first two calculations method on performance using the static (dynamic) method 图 10 动静态调度方式前两次性能对比 |

6.2.3 自适应优化

图 11给出了对第5.3节中提到的3个参数进行自适应优化的性能结果(不含调优时间), 并与采用静态调度方式、xssize=1536、从当前所需的第1个x进行加载静态buffer的方法进行了对比.从图中可以看出:自适应优化取得了比较明显的加速效果, 平均性能提升为44%, 最大的ecology1矩阵可达到6倍多, 这主要是动静态任务调度带来的加速.

|

Fig. 11 The performance of adaptive optimization 图 11 自适应优化效果图 |

6.2.4 性能结果

本文对选取的16个矩阵进行了测试, 图 12(a)展示了分别在主核和从核运行的结果, 主核版采用最原始的CSR格式SpMV实现.可以看出:测试的矩阵相对主核版均有不同程度的性能提升, 最高可达10倍多, 最低也有4倍多, 平均加速比为6.51倍.另外, 本文还测试了带宽利用率, 总访存量采用公式nz×12+(nrow+1)×4+nrow×8×2来计算.图 12(b)给出了测试矩阵的带宽利用率(总带宽按照实测带宽27.5Gb/s计算), 最高可达86.09%, 最低可达31.76%, 平均带宽利用率为47%.

|

Fig. 12 The performance of bandwidth efficiency of test matrices 图 12 测试矩阵的性能及带宽利用率 |

6.3 测试结果分析

从测试结果来看, 从核上SpMV的性能与其非零元的分布有很大关系.如果非零元分布的局部性特征比较明显, 那么本算法中动静态buffer的命中率较高, 从而整体性能较好.

目前, 整体的带宽偏低, 这是因为计算时采用了主核计算CSR格式SpMV的访存量, 而实际在从核计算时, 由于x的间接访问, 必然会引入x的额外访存.未来将进一步改进x的访存策略, 以提升整体性能.

对于一个特定的矩阵, 可通过观察分析其非零元的分布规律, 设计出特定的x的传输方案, 这样能尽可能地减少x的冗余访存, 进而提升带宽利用率和整体性能.

7 结论及下一步工作SpMV是众多科学与工程应用中经常调用的核心函数之一, 其性能至关重要.而CSR格式是使用最广泛的一种稀疏矩阵存储格式.本文针对申威处理器提出了一种CSR存储格式SpMV操作的通用异构众核并行算法, 该算法首先从任务划分、LDM空间划分方面进行精细设计.为了提升向量x的访存命中率, 本文提出了一套动静态buffer的缓存机制, 并分析了加载静态buffer起始位置对性能的影响; 对某些稀疏矩阵从核间负载不均衡的原因, 提出了一套动静态的任务调度方法以实现负载均衡.另外, 还分析了该算法中影响SpMV性能的几个关键因素, 并开展了自适应优化, 进一步提升了性能.

对于CSR格式的SpMV, 未来还需进一步考虑提升x访存命中率的方法, 比如利用该处理器的寄存器通信.还可以考虑根据稀疏矩阵的x访存特征对其进行分类, 对每一类的矩阵采用更加适合的访存方法, 以提升自适应性.另外还需考虑新的整体访存量更少的存储格式, 以提升整体性能.

| [1] |

Kourtis K, Karakasis V, Goumas G, Koziris N. CSX: An extended compression format for SpMV on shared memory systems. In: Proc. of the 16th ACM Symp. on Principles and Practice of Parallel Programming. San Antonio, 2011. http://dl.acm.org/citation.cfm?id=1941587

|

| [2] |

Sun XZ, Zhang YQ, Wang T, Long GP, Zhang XY, Li Y. Crsd: Application specific auto-tuning of SpMV for diagonal sparse matrices. In: Proc. of the 17th Int'l Conf. on Parallel Processing-Vol. Part Ⅱ (Euro-Par 2011). 2011. 316-327. http://dl.acm.org/citation.cfm?id=2033408.2033447&coll=DL&dl=GUIDE&CFID=419409108&CFTOKEN=83138306

|

| [3] |

Im EJ, Yelick K. Optimizing sparse matrix computations for register reuse in SPARSITY. In: Proc. of the Int'l Conf. on Computational Science. LNCS 2073, 2001. 127-136. http://www.springerlink.com/content/0932kfduv1kx1xac

|

| [4] |

Nishtala R, Vuduc R, Demmel, J, Yelick K. When cache blocking sparse matrix vector multiply works and why. In: Proc. of the Applicable Algebra in Engineering, Communication, and Computing. 2007. http://link.springer.com/article/10.1007/s00200-007-0038-9

|

| [5] |

Mellor-Crummey J, Garvin J. Optimizing sparse matrix-vector product computations using unroll and JAM. Int'l Journal of High Performance Computing Applications, 2004, 18: 225-236.

[doi:10.1177/1094342004038951] |

| [6] |

Willcock J, Lumsdaine A. Accelerating sparse matrix computations via data compression. In: Proc. of the 20th Annual Int'l Conf. on Supercomputing (ICS 2006). New York, 2006. 307-316. http://dl.acm.org/citation.cfm?id=1183444

|

| [7] |

Kourtis K, Goumas G, Koziris N. Optimizing sparse matrix-vector multiplication using index and value compression. In: Proc. of the 5th Conf. on Computing Frontiers. Ischia, 2008. http://xueshu.baidu.com/s?wd=paperuri%3A%28ee492d236f3bf105a7ebfa95c5ba90df%29&filter=sc_long_sign&tn=SE_xueshusource_2kduw22v&sc_vurl=http%3A%2F%2Fdl.acm.org%2Fcitation.cfm%3Fid%3D1366244&ie=utf-8&sc_us=10299234030662645419&sc_as_para=sc_lib%3A

|

| [8] |

D'Azevedo E, Fahey M, Mills R. Vectorized sparse matrix multiply for compressed row storage format. In: Proc. of the Int'l Conf. on Computational Science. 2005.

|

| [9] |

Williams S, Oliker L, Vuduc R, Shalf J, Yelick K, Demmel J. Optimization of sparse matrix-vector multiplication on emerging multicore platforms. In: Proc. of the 2007 ACM IEEE Conf. on Supercom-Putting. Reno, 2007. http://www.sciencedirect.com/science/article/pii/S0167819108001403

|

| [10] |

Vuduc R, Demmel J, Yelick K. OSKI: A library of automatically tuned sparse matrix kernels. In: Proc. of the SciDAC 2005, Journal of Physics: Conf. Series, 2005. http://ci.nii.ac.jp/naid/10026764860

|

| [11] |

Li JJ, Tan GM, Chen M, Sun NH. SMAT: An input adaptive auto-tuner for sparse matrix-vector multiplication. In: Proc. of the 34th ACM SIGPLAN Conf. on Programming Language Design and Implementation (PLDI 2013). 2013. 117-226.

|

| [12] |

Bell N, Garland M. Implementing sparse matrix-vector multiplication on throughput-oriented processors. In: Proc. of the Conf. on High Performance Computing Networking, Storage and Analysis. ACM Press, 2009. 18. http://xueshu.baidu.com/s?wd=paperuri%3A%2886ab30e5ad42deba0f848210bf06cc59%29&filter=sc_long_sign&tn=SE_xueshusource_2kduw22v&sc_vurl=http%3A%2F%2Fdl.acm.org%2Fcitation.cfm%3Fid%3D1654059.1654078&ie=utf-8&sc_us=16904681822754453526

|

| [13] |

Vazquez F, Fernandez J, Garzon E. A new approach for sparse matrix vector product on NVIDIA GPUs. Concurrency and Computation:Practice and Experience, 2011, 23(8): 815-826.

[doi:10.1002/cpe.v23.8] |

| [14] |

Monakov A, Lokhmotov A, Avetisyan A. Automatically tuning sparse matrix-vector multiplication for GPU architectures. In: Proc. of the Int'l Conf. on High-Performance Embedded Architectures and Compilers. Berlin, Heidelberg: Springer-Verlag, 2010. 111-125. http://www.springerlink.com/content/n2442u77n2333217

|

| [15] |

Choi JW, Singh A, Vuduc RW. Model-Driven autotuning of sparse matrix-vector multiply on GPUs. ACM Sigplan Notices, 2010, 45(5): 115-126.

[doi:10.1145/1837853] |

| [16] |

Ashari A, Sedaghati N, Eisenlohr J, et al. An efficient two-dimensional blocking strategy for sparse matrix-vector multiplication on GPUs. In: Proc. of the 28th ACM Int'l Conf. on Supercomputing. ACM Press, 2014. 273-282. http://doi.acm.org/10.1145/2597652.2597678

|

| [17] |

Yan S, Li C, Zhang Y, et al. yaSpMV:Yet another SpMV framework on GPUs. ACM SIGPLAN Notices, 2014, 49(8): 107-118.

[doi:10.1145/2692916] |

| [18] |

Pichel JC, Rivera FF, Fernández M, et al. Optimization of sparse matrix-vector multiplication using reordering techniques on GPUs. Microprocessors and Microsystems, 2012, 36(2): 65-77.

[doi:10.1016/j.micpro.2011.05.005] |

| [19] |

Tang WT, Tan WJ, Ray R, et al. Accelerating sparse matrix-vector multiplication on GPUs using bit-representation-optimized schemes. In: Proc. of the Int'l Conf. on High Performance Computing, Networking, Storage and Analysis. ACM Press, 2013. 26. http://xueshu.baidu.com/s?wd=paperuri%3A%28f91b6850fd1ee37a9ccf162f6f852281%29&filter=sc_long_sign&tn=SE_xueshusource_2kduw22v&sc_vurl=http%3A%2F%2Fdl.acm.org%2Fcitation.cfm%3Fid%3D2503234&ie=utf-8&sc_us=18024507869995616889&sc_as_para=sc_lib%3A

|

| [20] |

Sedaghati N, Mu T, Pouchet LN, et al. Automatic selection of sparse matrix representation on GPUs. In: Proc. of the 29th ACM Int'l Conf. on Supercomputing. ACM Press, 2015. 99-108. http://xueshu.baidu.com/s?wd=paperuri%3A%285ac557e66afd5ddbe626ec68f14d2894%29&filter=sc_long_sign&tn=SE_xueshusource_2kduw22v&sc_vurl=http%3A%2F%2Fdl.acm.org%2Fcitation.cfm%3Fid%3D2751244&ie=utf-8&sc_us=13465853919066897984

|

| [21] |

Ashari A, Sedaghati N, Eisenlohr J, et al. Fast sparse matrix-vector multiplication on GPUs for graph applications. In: Proc. of the Int'l Conf. for High Performance Computing, Networking, Storage and Analysis (SC 2014). IEEE, 2014. 781-792. http://www.oalib.com/paper/5285795

|

| [22] |

Guo D, Gropp W. Adaptive thread distributions for SpMV on a GPU. In: Proc. of the Extreme Scaling Workshop. University of Illinois at Urbana-Champaign, 2012. 2. http://dl.acm.org/citation.cfm?id=2462079

|

| [23] |

Liu X, Smelyanskiy M, Chow E, et al. Efficient sparse matrix-vector multiplication on x86-based many-core processors. In: Proc. of the ACM Int'l Conf. on Supercomputing. 2013. 273-282. http://dl.acm.org/citation.cfm?id=2465013

|

| [24] |

Tang WT, Zhao R, Lu M, et al. Optimizing and auto-tuning scale-free sparse matrix-vector multiplication on Intel Xeon Phi. In: Proc. of the 2015 IEEE ACM Int'l Symp. on Code Generation and Optimization (CGO). 2015. 136-145. http://xueshu.baidu.com/s?wd=paperuri%3A%2890144254eeedff7b0d82b0757b6c91e1%29&filter=sc_long_sign&tn=SE_xueshusource_2kduw22v&sc_vurl=http%3A%2F%2Fdl.acm.org%2Fcitation.cfm%3Fid%3D2738618&ie=utf-8&sc_us=4824601524567494968&sc_as_para=sc_lib%3A

|

| [25] |

Kreutzer M, Hager G, Wellein G, et al. A unified sparse matrix data format for efficient general sparse matrix-vector multiplication on modern processors with wide SIMD units. SIAM Journal on Scientific Computing, 2014, 36(5): C401-C423.

[doi:10.1137/130930352] |

| [26] |

Liu W, Vinter B. CSR5: An efficient storage format for cross-platform sparse matrix-vector multiplication. In: Proc. of the ACM Int'l Conf. on Supercomputing. 2015. 339-350. http://www.oalib.com/paper/4072566

|

2018, Vol. 29

2018, Vol. 29