1958年,美国物理学家Jack Kilby发明了世界上第一个集成电路,这项技术改变了整个世界,并且一直影响至今,Kilby也因此于2000年获得了诺贝尔物理学奖[1, 2].随着半导体技术的发展,电子元器件特征尺寸越来越小,芯片集成度遵循摩尔定律不断提高.为了有效地利用和管理越来越多的片上资源,用系统的思想进行芯片设计非常必要.基于总线结构的片上系统(system on chip,简称SoC)[3]成功地将多个具有不同功能的IP核(intellectual property core)集成于同一块芯片上,IP 核之间可以独立地执行不同的任务,实现IP核间的并行计算,从而提升了处理器的计算能力[4].但是,随着芯片上集成的IP核数目的增加和用户对嵌入式电子产品功能与性能需求的日益增长,总线型结构无法满足众多的实际需求,因而产生了片上网络(network-on-chip,简称NoC).NoC的核心思想是:将网络技术应用到芯片设计之中,使得IP核之间的数据交换通过路由器来实现[5].NoC结构与总线结构相比,不仅具有较好的可扩展性、可重用性,而且可以在支持并行通信的同时,实现全局异步局部同步(globally asynchronous locally synchronous,简称GALS)的时钟控制[6],从体系结构上彻底解决了总线结构带来的单一时钟问题.随着芯片上IP核数的增加,芯片的面积、功耗不断增大,芯片中全局导线变得越来越长,限制了工作频率的提升空间,因而,芯片开始向三维发展.近年来,随着三维集成电路(three-dimensional integrated circuit,简称3D IC)的发展,三维片上网络(three-dimensional network-on-chip,简称3D NoC)以其更短的全局互连、更高的封装密度、更小的体积等诸多优势[7],逐渐成为NoC领域的主要研究方向.目前,关于3D NoC的研究已经取得了很多成果,但仍处于探索阶段.对国内外关于3D NoC的研究进展进行较为全面的总结,对未来3D NoC的深入研究具有重要意义.

1 三维片上网络简介 1.1 二维片上网络随着SoC规模的扩大和复杂度的增加,片上互连成为系统性能的瓶颈[8],其主要原因是总线结构的局限性.为解决此问题,2001年,Dally等人首次提出采用分组路由方式进行片内通信的思想,并将这种通信方式称为NoC[9, 10].NoC就是在一个芯片上集成数字电路、模拟电路、射频(radio frequency,简称RF)、内存的接口电路等,使系统的速度更快、集成度更高,并且功耗、成本和体积也都大为降低[11].2D NoC中最常见的2D Mesh架构如图 1所示[7].

|

图 1 4×4的2D Mesh架构 Fig.1 4×4 2D Mesh architecture |

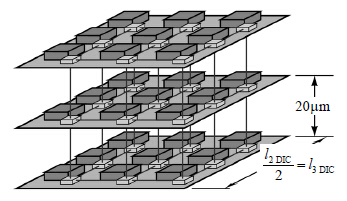

随着芯片集成度的进一步提高,受二维布局条件的限制,2D NoC难以保证关键部件相邻,难以缩短关键路径长度及减少信号延迟;与此同时,基于三维封装(three-dimensional packaging)技术的3D IC技术有了长足发展,为此,3D NoC应运而生.2005年,Liu等人首次提出了3D NoC的概念[12],其核心思想是将2D NoC与3D IC融合起来,最常见的3D Mesh架构如图 2所示[7].

|

图 2 3×3×3的3D Mesh架构 Fig.2 3×3×3 3D Mesh architecture |

3D NoC采用将多个具有二维结构的芯片用三维封装的方式封装成一个芯片,芯片与芯片之间主要依靠硅通孔技术(through-silicon-via,简称TSV)互连.硅通孔技术是通过在芯片和芯片之间、晶圆和晶圆之间蚀刻出垂直通孔,通孔中注满金属以实现芯片之间互连的最新技术[13].与以往的集成电路(integrated circuit,简称IC)封装技术不同,TSV能够使3D NoC在三维方向堆叠的密度最大、外形尺寸最小、数据传输速度更快、系统功耗更低.此外,芯片的可维护性也会增强,即使某层硅片出现故障,也可以对其单独进行修复.3D NoC的出现是IC技术中突破性的新技术,也是IC发展的一个里程碑.

2 三维片上网络研究现状国内外关于3D NoC的研究方兴未艾,有许多大学和研究机构加入到这项研究之中,公开发表了大量以3D NoC为主题的学术论文,研究开发了3D NoC仿真平台,极大地促进了该领域的发展.

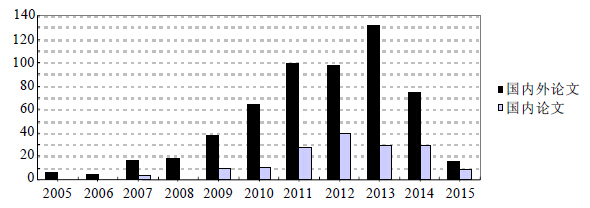

2.1 国内外研究概况 2.1.1 3D NoC相关论文最早有关3D NoC的论文公开发表于2005年[12, 14],截至2015年3月份,可查到的有关3D NoC研究的论文有500余篇.每年发表的3D NoC相关论文数如图 3所示,其中,深色为国内外全部论文数,浅色为国内期刊发表的论文数.由图 3可见:从2005年~2013年,每年发表的相关论文数呈递增趋势;2014年,3D NoC研究趋于平稳.国内关于3D NoC的研究起步较晚,但近几年也逐渐成为我国学术领域一个重要的研究方向.

|

图 3 每年发表的3D NoC相关论文数 Fig.3 Papers published every year related to 3D NoC |

国内许多研究机构和大学都开展了3D NoC方面的研究,国家自然科学基金自2009年开始对3D NoC相关项目进行资助,至今共资助10项相关项目,研究内容涉及拓扑结构、通信技术、容错技术以及热均衡等多个方面,见表 1.

| 表 1 国家自然科学基金资助的3D NoC项目 Table 1 3D NoC project funded by the National Natural Science Foundation |

我国关于3D NoC方面的研究相对发达国家起步较晚,但近年来也取得了许多研究成果,为我国未来的三维集成电路和三维芯片产业发展奠定了重要基础.南京大学李丽等人在3D NoC方面的研究较早,他们在研究过程中提出了一个新的体系结构——hybird hierarchical architecture[15],并且证明了该体系结构可以明显地提高系统性能.此外,他们还设计了关注于延迟的映射算法RMGA和基于蚁群算法的DACA算法[16, 17].合肥工业大学张多利等人提出了基于System C的3D NoC仿真器设计[18]和基于温度梯度的3D NoC路由算法[19].南京航空航天大学葛芬等人提出一种基于Spidergon的通用三维拓扑结构及其拓扑生成方法[20].电子科技大学陈亦欧等人对3D NoC拓扑结构进行研究[21],并提出了基于De Bruijn图的架构[22, 23].西安电子科技大学刘有耀等人对NoC拓扑结构与通信方法进行了研究,对典型的3D NoC架构进行了总结,并提出了3种3D NoC的架构,包括三维超立方体双环架构、三维Torus连接的Petersen图架构、三维长方形扭花环网格架构[24].国防科学技术大学钱悦等人的研究表明:3D NoC因拓扑维度的增加而缩短了通信距离,极大地提升了网络的平均通信性能[25].南京邮电大学范敬雯等人总结了多种3D NoC架构的性能[26],分析了适用于3D NoC的路由技术,并对3种适合3D NOC的路由算法进行了仿真.上海交通大学付宇卓等人搭建了一个三维环境下的仿真平台[27],研究了3种3D Torus网络拓扑结构(Symmetric Torus,Stacked Torus和X-Torus结构)的性能,并通过均衡负载模式、对称随机负载模式分析评价了这3种3D Torus网络的零负载延迟和吞吐率[28].天津工业大学张大坤等人对3D NoC路由算法和拓扑结构进行了系统的分析[29, 30],提出了一种改进的基于粒子群算法的3D NoC优化布局算法和一种新型的N维Mesh容错路由方案[31].合肥工业大学欧阳一鸣等人对NoC测试进行研究[32],提出了簇式3D NoC通信压力弱化策略[33]和3D NoC TSV复用容错策略[34],还提出了3D NoC故障及拥塞感知的容错路由器设计[35]以及3D NoC中柔性可配置的高可靠路由器设计[36]、基于虚通道故障粒度划分的3D NoC容错路由器设计[37]和面向非全互连3D NoC可靠通信的分布式路由算法[38].

2.1.4 国外有代表性的研究工作国际上关于3D NoC的研究起步较早,在网络拓扑和路由器结构方面,美国宾夕法尼亚州立大学(Pennsylvania State University)Xie等人的研究较为深入,主要研究的是系统级仿真、动态虚通道、路由器结构、多维映射和布局布线的影响等,他们在3D IC设计以及系统架构方面取得了重要的研究成果[39, 40, 41, 42].Dongkook等人主要研究布局布线对处理器和存储结构的影响[41];Sun等人充分研究了多核架构下的共享组L2 Cache的布局优势[42],在多层缓存块和处理核之间分别采用了基于核分布和均匀分布的两种方法.仿真实验结果表明,前者可以获得更好的性能.美国加州大学(University of California)Lin等人在3D NoC路由方面作了较多的研究,提出了多层3D NoC架构、阐述了相关设计问题[43, 44, 45, 46, 47].芬兰图尔库大学(University of Turku)Xu等人的研究主要涉及从二维到三维性能评价函数的变化和对之前提出的3D NoC架构的总结,并提出了新的架构和路由算法[48, 49, 50, 51, 52, 53, 54].伊朗伊斯兰阿萨德大学(Islamic Azad University)Reza等人提出了一个提高容错和通信负载的适合多媒体应用程序的拓扑和多路径路由,还提出了一个新的架构——Kautz mesh和一个基于Shuffle-exchange拓扑的有效三维布局,并对它们的性能进行了仿真实验[55, 56, 57].台湾大学Chao等人对3D NoC的热影响进行了分析,提出了热敏路由共享体系结构、基于非稳定非规则的传输层辅助路由和通信、热敏的实时热管理方案[58, 59, 60].香港科技大学(Hong Kong University of Science and Technology)Ye等人对三维光学片上网络的设计和热力学分析进行了相关的研究[61, 62, 63].日本庆应义塾大学(Keio University)Hiroki等人对无线3D NoC进行了研究,并取得了相应的研究成果[64, 65, 66, 67, 68].

2.2 仿真平台计算机仿真是继科学实验和理论指导之后,科学探索和工程实践的第三推动力,它在3D NoC的研究中显得尤其重要.目前,国内外在3D NoC的研究中,大部分理论验证和实验都是在计算机仿真平台上进行的,其主要原因是:专门设计一个实际的3D NoC芯片来验证有关设计理论、设计方案以及算法的优劣,其成本极高、难以实施.特别是随着3D IC和3D NoC技术的发展,三维芯片上集成的IP核数不断增加,异构3D NoC的需求也不断增加,使得3D NoC设计工作变得越来越复杂,完成3D NoC设计所花的时间和成本急剧增加.3D NoC的研究始于2005年[12],许多问题尚处于探索之中,目前尚未有功能齐全的商用3D NoC仿真平台.许多研究者针对自己的研究开发了适合某些方面的3D NoC仿真平台,极大地推动了3D NoC的发展,下面介绍4个有一定代表性的3D NoC仿真平台.

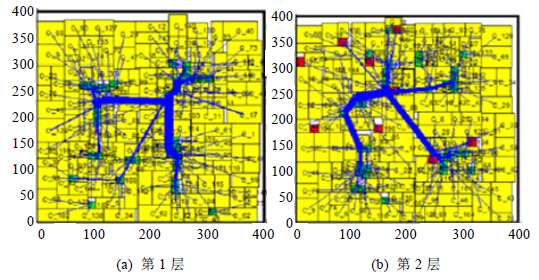

2.2.1 VNOC3[69]VNOC3是由美国北达科他州立大学de Paulo等人研发的、用于研究2层和3层3D NoC的仿真框架,该框架是在一个低版本VNOC(一个周期精确的NoC仿真器)和一个B*树布局规划器的基础上开发的.对于3层架构的NoC,它采用hMetis划分器对任务图进行划分.框架还包括GUI图形功能和可以用来产生新的跟踪文件的隐藏选项.该工具虽然是在Linux系统Fedora 8上开发的,但也可以在Windows系统中编译运行.

2.2.2 Access Noxim[70]Access Noxim是由台湾大学Jheng等人开发的、将网络模型、功率模型和热模型相结合的3D NoC仿真平台,该仿真平台将Noxim和HotSpot相结合,并采用Intel的80-core处理器的功率模型.为了与HotSpot (HotSpot提供架构级热模型)进行结合,3D NoC仿真器需要将其架构级布局和功率跟踪转换为芯片级物理布局和功率追踪.首先添加基础三维路由器模型和垂直开关路由,将Noxim进行扩展来产生基于用户定义维数的3D NoC架构,之后插入一个模型,将架构级布局直接转换成物理布局.

2.2.3 Nigram[71]Nigram是由英国南安普顿大学和印度Malaviya国家技术研究院共同研发、周期精确的3D NoC仿真器,能够仿真不同拓扑结构的路由算法和应用程序.Nigram是一个可扩展、模块化、基于System C的仿真器,允许在3D NoC设计的不同阶段(拓扑、交换技术、虚拟通道、缓冲参数、路由机制和应用程序等)尝试不同的可用选项;除了内置功能,对于新的应用程序和路由算法,可以很方便地进行扩展;对于给定的选项设置,仿真器可以输出延迟、吞吐量等性能指标.

2.2.4 gpNoCsim[72]gpNoCsim是由美国罗切斯特大学Hossain等人研发的基于Java、支持不同3D NoC架构(Mesh,Torus, Butterfly Fat Tree等)评估的通用仿真器,其模块化的设计使其便于接受新的架构.仿真器源代码和手册可以在www.buet.bd/cse/research/group/noc/上进行下载.

3 三维片上网络研究的关键问题 3.1 关键问题简介3D NoC的研究涉及许多方面,其中要解决的关键问题可归纳如下:网络拓扑结构、路由机制、性能评估、容错、功耗、映射、测试、交换技术、服务质量、流量控制以及资源网络接口等.

(1) 网络拓扑结构.3D NoC网络传输消息的能力主要依赖于拓扑结构,它对网络延迟、吞吐量、面积、容错以及功耗等都有很大影响,同时对设计策略和内核到网络节点的映射起着重要的作用.选择合适的3D NoC拓扑结构,是3D NoC设计中非常关键的问题之一;

(2) 路由机制.路由是确定一个消息从源节点到目的节点的路径机制.区别于总线结构,3D NoC的一个重要特征是采用包交换路由.包交换既可以在源节点上实现路由,也可以在每一跳节点上实现路由,相应地称为源路由和分布式路由.无论是哪类路由算法,都应该有效地解决死锁、活锁和饥饿等问题;

(3) 性能评估.性能评估是3D NoC设计的一个重要方面.为了比较不同的3D NoC结构,必须使用一套标准的性能评价指标.评估一个3D NoC的性能主要包括以下4个方面[73]:吞吐量、延迟、面积和功耗等;

(4) 容错.3D NoC容错对象主要包括硬错和软错两方面:硬错,即芯片内部物理缺陷,包括路由器本身和路由器之间连线等缺陷;软错,即芯片内部数据传输过程中,由于各种原因(如串扰、噪声、宇宙射线等)导致的信号翻转.容错性问题是一个系统问题,常见的容错方法主要是从物理层、数据链路层和网络层3个方面着手;

(5) 低功耗.3D NoC的功耗与拓扑结构、路由器结构、路由算法等密切相关.拓扑结构直接影响到IP核间的通信,对整个芯片的功耗和吞吐率优化起到非常重要的作用.路由算法的目标是正确、有效地传输数据包.良好的路由算法可以提高网络的性能、降低功耗和延时、保证3D NoC系统的容错性[74];

(6) 映射算法.映射是在给定任务图、设计约束(延迟和功耗等)和IP核库的基础上,将每个任务分配到合适的IP核上,安排每个IP核上的任务执行顺序,然后再决定每个IP核在3D NoC拓扑结构中的位置;

(7) 测试.芯片的复杂度和集成度越来越高,测试成本比设计和制造成本更高、耗费时间更长.因此,如何更高效地完成3D NoC测试已成为研究热点[75].3D IC具有比传统的平面IC更高的性能,在3D IC上进行有效的测试架构设计和优化技术可以减少3D IC的测试代价[76];

(8) 交换技术.交换技术决定交换节点何时、如何连接其输入与输出端口,交换技术包括包交换和电路交换两种主要类型;

(9) 服务质量.服务质量(quality of service,简称QoS)被定义为网络提供给IP核需要的服务数量,包含两方面内容:① 定义了某一数量的服务;② 服务协商.服务应该具有高吞吐量、低延迟以及低功耗等特点,协商是指在IP核需求的服务与网络提供的现有服务之间实现平衡;

(10) 流量控制.在3D NoC领域,流量控制被特定用于控制交换节点间、端到端之间的传输协议的业务量.通过避免缓冲区溢出及丢包,这些协议提供了平滑通信量策略;

(11) 资源网络接口.资源网络接口(resource network interface,简称RNI)是资源(IP核)与网络间的接口,通过RNI,IP核可以用最小的代价使用网络.同时,IP核和网络资源都可以重用.RNI在功能上可以分为两个部分:其一,连接网络的部分,与IP核无关;其二,连接到IP核,与资源相关;

(12) 其他.3D NoC还涉及节点布局、性能仿真以及定时等方面的研究.

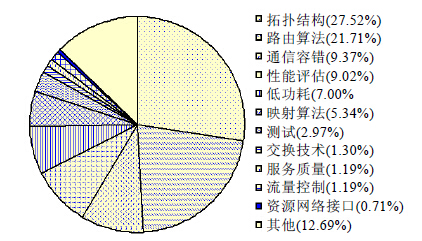

3.2 相关研究成果一览自2005年3D NoC首次被提出,可查到的有关3D NoC关键问题研究公开发表的各方向的学术论文所占比例如图 4所示.拓扑结构和路由算法是两个重要的研究方向,其论文数分别占3D NoC相关总论文数的27.52%和21.71%.此外,还有通信容错、性能评估、低功耗、映射算法、测试、交换技术、服务质量、流量控制以及资源网络接口等研究方向,论文所占比例依次为9.37%,9.02%,7.00%,5.34%,2.97%,1.30%,1.19%,1.19%和0.71%;其他方面的研究涉及更多问题,论文所占比例为12.69%.

|

图 4 3D NoC各关键问题研究领域发表论文所占比例 Fig.4 Proportion of related papers of each key problem in 3D NoC |

自2005年第一篇关于3D NoC的学术论文发表以来,国内外有许多科技工作者对这一领域的关键问题进行了大量的研究,并取得了许多研究成果.

4.1 拓扑结构综合国内外目前的研究成果,3D NoC拓扑结构可归纳为63种,可以从不同角度进行分类.由于3D NoC主要解决通信瓶颈问题,可以从通信角度将3D NoC拓扑结构分为9大类,如图 5所示[30].

|

图 5 3D NoC拓扑结构分类 Fig.5 3D NoC topology classification |

基于Mesh的3D NoC拓扑结构包括:直接扩展的3D Mesh[77]、堆叠3D Mesh[77]、纤毛3D Mesh[77]、真正3D crossbar[78]、低功率异构3D NoC[79]、三维直接访问多端口缓冲架构[80]、层复用3D NoC[47]、MIRA[81]、基于3D Mesh的双链路互连架构[82]、低基数低直径3D互连网络拓扑结构[83]、基于双向双同步垂直通道的3D NoC架构[84]、垂直部分连接的3D NoC拓扑结构[85]、基于异构布局的3D NoC拓扑结构[69]以及Tiny NoC[86]等.其中,直接扩展的3D Mesh是将2D Mesh直接扩展到三维空间中;堆叠3D Mesh是分组交换网络与总线的混合体,通过横跨芯片整个垂直方向的总线将多个2D Mesh堆叠起来;纤毛3D Mesh是每个路由节点与多个IP核相连的3D Mesh结构,网络的路由与通信被限制在路由节点所在的各层芯片内,每个路由节点负责多个IP核的传输与接入.

4.1.2 基于Torus的3D NoC拓扑结构基于Torus的3D NoC拓扑结构包括:对称3D Torus[87]、堆叠3D Torus[87]、3D X-Torus[87]以及压缩的3D Torus 架构[88]等.其中,对称3D Torus是一种完全对称的拓扑结构,每个节点的设置都相同,因此所有路由器微结构均相同;堆叠3D Torus是将多层2D Torus结构进行堆叠、每层顺次连接得到的;3D X-Torus是将2D Torus堆叠起来,其节点路由器在传统NoC路由器设计的基础上新增了一个端口,用于连接纵向路由器,该路由器与纵向每一列的节点相连.

4.1.3 Cluster Mesh拓扑结构Cluster Mesh拓扑结构包括:Cluster Mesh[89]、基于网格和基于环的拓扑结构[90]、基于Cmesh和TSV的3D NoC拓扑结构[91]、三维多聚类片上网络的混合分层架构[15]、采用先进层间总线架构的基于分簇拓扑的3D NoC架构[92]、基于分簇拓扑的三维堆叠架构[93]、三维递归网络拓扑[94]以及基于部分重叠集群的3D NoC拓扑结

构[95]等.其中,Cluster Mesh应用一个新的垂直互连序列方案,通过垂直路由器共享垂直链路来降低TSV的数量;基于网格和基于环的拓扑结构都有3层,每层包含16个节点,每个IP核通过路由器连接网络,每个路由器依次与相邻路由器连接,每4个节点组成一个聚类,其中一个节点为聚类头节点;基于Cmesh和TSV的3D NoC拓扑结构利用光学互连(optical interconnection system,简称OIS)和电气互连系统(electrical interconnection system, 简称EIS),克服了Cmesh拓扑的局限性,通过降低路由器密度比率提高了吞吐量.

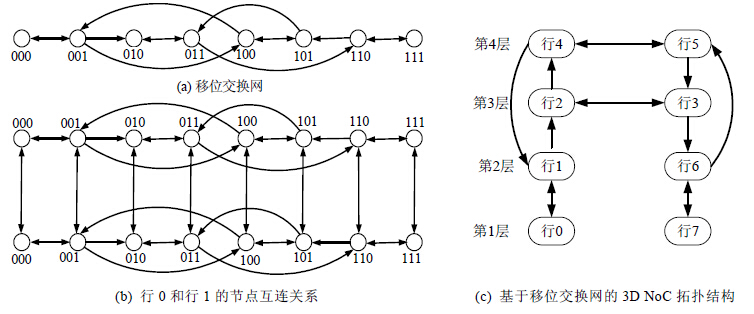

4.1.4 基于移位交换网络的3D NoC拓扑结构传统的移位交换网如图 6(a)所示,其中,节点地址用二进制表示.

|

图 6 基于移位交换网的3D NoC拓扑结构 Fig.6 3D NoC based on shuffle-exchange topology |

相邻节点的地址满足循环移位或者交换(地址的最低位取反)关系基于移位交换网络的3D NoC拓扑结构,包括:基于移位交换网的3D NoC拓扑[96]、基于桥接De Bruijn图的3D NoC[23,97-99]、基于环接De Bruijn图的3D NoC[23,97-99]、基于双De Bruijn图的3D NoC[23,97-99]、基于增强桥接De Bruijn图的3D NoC[100]以及Kautz Mesh[57]等.其中,

● 基于移位交换网的3D NoC拓扑如图 6(c)所示,每一行表示一个一维的移位交换网.例如,第0行有8个节点,每个节点与第1行中的对应节点双向连接;其他节点也按照类似的方式连接,如图 6(b)所示;

● 基于桥接De Bruijn图的3D NoC芯片内网络采用直径小、节点度固定、路由灵活的De Bruijn图[101]作为拓扑,芯片之间采用桥结构进行连接;

● 基于环接De Bruijn图的3D NoC芯片内网络采用De Bruijn图,芯片之间采用双环将三维结构上的各个节点连接起来以实现容错.

4.1.5 基于超立体结构的3D NoC拓扑结构基于超立体结构的3D NoC拓扑结构包括:三维超立方体结构[102]、三维超Mesh结构[103]、三维超Torus结构[104]、三维超立方体双环拓扑结构[105, 106]、3D Torus连接的Petersen图拓扑结构[24]、三维长方形纽花环网络拓扑结构[24]、环嵌入超立方体结构[107]、分层Torus网络[108]以及对称圆环Torus网络[109]等.其中,三维超立方体结构如图 7所示,它具有对称性好、网络直径短以及可扩展性好等优点,但超立方体在二维芯片中不易布局,而在三维芯片中可以很方便地进行布局;三维超Mesh结构是通过Mesh和超立方体交叉得到的,继承了超立方体和Mesh两者的优点,同时还提高了超立方体的可扩展性、降低了节点度和成本;三维超Torus结构以三维超立方体架构为基本模块,并结合了Torus网络,节点度为4,节点和边是对称的,并且具有可扩展性.

|

图 7 四维超立方体拓扑结构 Fig.7 Four-Dimensional hypercube topology |

基于正多边形阵列的3D NoC拓扑结构包括:蜂窝状3D NoC拓扑[110]、基于Spidergon的通用三维拓扑结构[111]以及3D Octagon双环拓扑结构[112]等.其中,蜂窝状3D NoC拓扑是由正六边形堆叠起来的拓扑结构,除顶层和底层外,其他内部层上的每个路由器包含两个纵向连接,用于连接与其上下相邻的路由器,如图 8所示.基于Spidergon的通用三维拓扑结构顶点对称,提供了设计的方便性和规则性,使它适合多种互连模型,降低了布局的复杂性.另外,低节点度和较小的网络直径使得延迟降低;3D Octagon双环拓扑结构的最大特点是网络距离短、任何两个节点之间通信最多只需要两步即可完成,并且布线复杂度比交叉开关结构低很多.

|

图 8 三维蜂窝Mesh架构 Fig.8 Architecture of 3D honeycomb Mesh network |

面向应用的组合拓扑结构包括:XNoTs[113]、SunFloor 3D[114]、3D处理器-存储器架构[115]、3D光学NoC拓扑结构[62]、3D存储器网络架构[116]、应用于特定程序的3D NoC结构[45]、CMP感知的特定应用的3D NoC[117]、基于聚类的功率感知拓扑结构[118]以及最小重构三维堆叠纳米光子片上网络架构[119]等.其中,XNoTs拥有连接不同层和它们的核的交叉开关,每个二维层都是可以单独自定义的,其形式包括Mesh,Tori以及Tree等; SunFloor 3D用于合成专用的3D NoC拓扑结构,配置和布局3D层上的网络元件,生成的拓扑结构与标准的拓扑结构相比,显著降低了功率和延迟;CMP感知特定应用的3D NoC拓扑结构如图 9所示,实验结果表明,这种拓扑结构比TSV高度变化平均减少17.9%,跳数减少15%,总体线长缩短2.3%.

|

图 9 CMP感知的特定应用的3D NoC Fig.9 CMP-Aware application-specific 3D NoC |

容错3D NoC拓扑结构包括:局部虚拟信道共享架构[120]、同构并行集中Mesh结构[121]、特定应用程序容错3D NoC拓扑合成[122]以及基于Mesh的容错3D NoC拓扑结构[123]等.其中,局部虚拟信道共享架构,实现了自主的虚拟信道缓冲共享;同构并行集中Mesh结构可以动态地适应网络中的工作状态,通过使用部分低通信率的网络降低功耗,通过使用高通信率的网络提高性能.

4.1.9 其他类型的3D NoC拓扑结构还有一些3D NoC拓扑结构,如:基于树图的3D NoC[77]、三维合成CLOS NoC[124]、序列化垂直通道3D NoC[125]、新型3D NoC拓扑结构模型Shuttle[126]、基于蝶形胖树拓扑的低延迟扩展3D NoC[127]以及小功耗分层3D NoC拓扑[128]等.蝶形胖树的拓扑结构如图 10(a)所示,它通过多个层次的交换网络把各IP核连接起来,网络直径小,但是交换网络结构复杂.Stanley等人提出的基于蝶形胖树的3D NoC如图 10(b)所示,序列化垂直通道3D NoC可以导致更好的TSV热分布,可以降低峰值温度,同时由于降低了阻塞,使多个层之间的IP核可以更有效地分布.各类3D NoC拓扑结构性能比较见表 2.

|

图 10 蝶形胖树及其三维架构 Fig.10 BFT and its 3D architectures |

| 表 2 拓扑结构性能比较一览表 Table 2 Performance comparison of different topologies |

综合分析可查到的有关3D NoC路由算法的学术论文,将目前的3D NoC路由算法进行归类总结,并将其分成无关路由算法、自适应路由算法和其他路由算法这3类[29].

4.2.1 无关路由算法无关路由算法是一种常见的路由算法,它的路由路径只与源节点地址和目的节点地址有关,在给定源节点和目的节点地址的前提下,路由的下一跳节点随机决定,而与当前的网络状态无关.无关路由的优点是路由算法简单,在网络低拥塞环境下能够获得较低的延迟.但是,由于其不能响应动态的网络状态变化,所以当网络拥塞增加时,性能迅速降低.

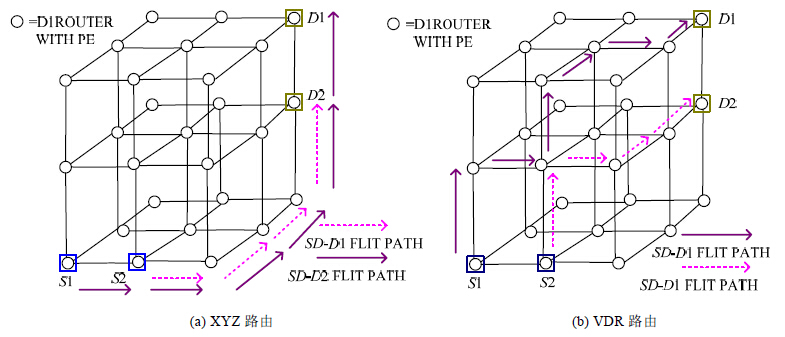

确定性维序XYZ路由算法[129]、RPM无关路由算法[46]、LA-XYZ路由算法[130]、VDR路由算法[131]、USM路由算法[132]以及PROM3D路由算法[133]等都属于无关路由算法.在维序路由算法中,每个数据包每次只在一个维上路由,当在该维上到达了目的坐标之后,才按由低维到高维的顺序在其他维上路由.使用RPM无关路由算法通常会得出两个合适的路径:Z-XY-Z和Z-YX-Z路径,路由过程中共需要3次转弯.LA-XYZ路由算法是在XYZ算法的基础上提出的,也被称为最小限度的维序路由算法.VDR路由算法旨在三维空间中建立源处理单元到目的处理单元的对角链,VDR算法和XYZ路由算法的对比如图 11所示.USM路由算法包括3个部分:ZXYXZ路由、XYZYX路由和YZXZY路由.其中,每个部分被选中的机会都是均等的,并且3个部分都使用最短路径路由.PROM3D路由算法在每个节点局部地选择下一个可用节点,并且在每一个节点上随机选择下一跳节点.

|

图 11 XYZ和VDR之间的对比 Fig.11 Comparison between XYZ and VDR |

自适应路由算法是指数据包的路由路径不仅与源节点和目的节点的地址有关,还要考虑网络的即时流量和拥塞状况,即:源节点与目的节点地址相同的数据包在不同的网络状态下,它们的路由路径也可能不同.自适应路由算法的优点是避免了网络拥塞,可以获得更高的网络带宽和吞吐量;但是路由逻辑复杂、需要的资源较多、实现起来较困难,并且在低拥塞的情况下开销较大,而且还存在死锁问题.

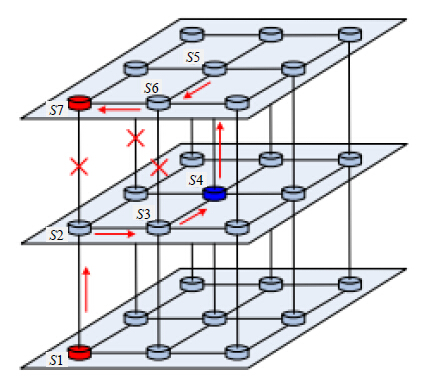

目前,主要的自适应路由算法有:LFDRA路由算法[134]、4NP-First路由算法[135]、AFRA路由算法[136]、TDAR路由算法[137]、TPRA路由算法[138]、TTAR路由算法[139]、TFRA路由算法[140]、自适应层间路由算法[141, 142]、SBSM和DBSM算法[143]、Elevator-First路由算法[144]、DBFALI路由算法[145]、可降解的路由算法[146]、无死锁的平面平衡的自适应路由算法[147]、DyXYZ路由算法[148]、偏转路由方案[149]、Redelf路由算法[150]、TAAR[151]、TTABR[152]、使用曼哈顿距离策略的容错路由算法[153]、一种有效的完全自适应容错路由算法[154]、DQP路由算法[155]、ATRR[156]、高度自适应和拥塞感知的路由算法[157]、3D-RPM[158]、三维递归超图哈密顿连接网络无死锁路由算法[159]、双向路由[160]、面向非全互连3D NoC可靠通信的分布式路由算法[161]、HLAFT[162]以及基于层次化片上网络的混合多播路由算法[163]等.其中,LFDRA路由算法的路由设计主要分为两步——同层数据包路由和跨层数据包路由,该算法只使用一层路由表和两个TSV状态向量,就可以做出有效的路由以避免垂直链路和水平链路故障,算法示意如图 12所示;4NP-First算法通过虚拟信道技术来避免死锁,并且分割出了两个虚拟信道,一个分配给4N-First数据包,另一个分配给4P-First数据包;AFRA算法是一种允许垂直链路出现故障的低成本高性能可靠路由算法;TDAR算法是带有垂直链路带宽限制的适用于3D Mesh的自适应路由算法;TPRA算法是考虑到功耗的三维自适应路由算法;TTAR算法是一种自适应路由算法,用于缓解由于短暂的温度控制节流造成的通信拥塞,主要由自适应路由功能和节流意识选择组成;TFRA算法是考虑到功耗的免死锁三维全动态3D NoC路由算法,该算法以传统2D NoC奇偶转弯模型为基础,将三维路由空间划分为8个象限,针对每个象限制定相应的路由策略.

|

图 12 LFDRA路由算法示意 Fig.12 Example of LFDRA routing algorithm |

电子科技大学张宇阳等人提出了DFTR(dual flit transmission rate)路由架构[164],该架构可以获得垂直方向上更快的传输速率.同时,该架构使用虚拟输出队列(virtual output queue,简称VOQ)代替原来的虚拟信道,降低了开关延迟,并提高了性能.台湾大学Huang等人提出了热敏共享路由架构[59],该架构移除了所有顶层的路由,只使用总线结构连接顶层,从而避免了热影响.这种路由架构在热影响下的性能超过了许多已有的设计,在85°C时能获得1.4倍的数据包、在80°C时能获得2倍的数据包,并且该架构有效地降低了跳步数.台湾大学Chao等人针对非静止、不规则的Mesh(non-stationary irregular mesh,简称NSI-mesh)拓扑提出了一个传输层辅助路由方案——TLAR(transport layer assisted routing)[58].NSI-mesh是一种时变的不规则拓扑,主要有两点特征:其一,当一个路由被限流时,其上面的所有路由被限流;其二,若有一个路由未被限流,则所有的路由均未被限流.此外,Chen等人提出了VTBR(vertical traffic balance routing)路由方案[165],该方案中包含了两方面的技术,分别是无关的向下层选择技术和释放横向向下转弯模型,该方案比之前提出的TLAR在吞吐量和通信负载平衡方面均有显著的提高.美国科罗拉多州立大学Salas等人提出了一个新的带有路由中心分解和共享虚拟信道缓存的路由结构,被称作Roce-Bush路由[166],该路由由路由中心、物理优化、分解仲裁器和方向性缓存这4部分构成.

4.3 性能评估性能评估是3D NoC设计中需要考虑的一个重要因素,为了比较不同的3D NoC结构,必须使用一套标准的性能评价指标.评估一个3D NoC的性能主要包括以下几个方面:吞吐量、延迟[167-169]、面积[54, 170]和功耗[171, 172].根据评估对象和评估方法的不同,可将性能评估分为以下两类:基于特定拓扑结构的性能评估和基于评估方法的性能评估.

4.3.1 基于特定拓扑结构的性能评估性能评估主要是在特定条件下针对特定拓扑结构的评估.例如:在均衡负载模式和对称随机负载模式下3D Torus网络延迟和吞吐率的评估[173],k-ary-2-mesh网络及其对应的三维网络在最差情形下的通信性能评估[25], 3D超立方体结构在均匀负载、局部负载和热点负载模式下与3D Mesh结构的性能比较[174],3D NoC轻度混合SRAM NUCA的性能和网络能量评估[172],存储高效3D NoC架构的性能和功耗分析[175],3D堆叠可重构纳米光子互连的可伸缩性和性能评估[176].

4.3.2 基于评估方法的性能评估性能评估的方法有很多,如:基于网络演算对片上网络进行系统建模和性能分析[177],通过数学分析和软件仿真,对片上网络的两种常见拓扑结构(Torus结构和Mesh结构)在3D NoC中的通信性能(传输延时和吞吐量)和面积开销进行评估[178];利用实验仿真,在均匀负载、局部负载和热点负载模式下将超立方体结构与3D Mesh结构进行网络性能与功耗的比较[179].

4.4 低功耗NoC的互连网络功耗有如下定义:NoC内节点之间由数据交换所产生的功耗[180].研究人员最先提出了一种描述NoC通信功耗的模型,叫“位”功耗模型,用来评估1bit数据经由交换开关传输后的通信功耗[181].后来为了更精确,定义了一种更好的模型,叫“flit”功耗模型,它是求解1flit数据在互连网络中传输时所消耗的功耗[182].但这两种模型都没有考虑时钟树的功耗.而随着集成电路规模的不断扩大,时钟树的功耗已经在芯片总功耗中占有相当大的比例,忽略它会使得功耗评估产生很大误差,所以,西安电子科技大学黄岗等人在第2种功耗模型的基础上加入了对时钟树功耗评估的模型[183],提高了模型的准确度.功耗分析主要是分析特定拓扑结构、路由算法、映射算法以及布局等对功耗的影响.

4.4.1 基于拓扑结构的功耗分析巴西UFRGS信息学研究所Matos等人提出了一种小功耗分层3D NoC拓扑[128],因为一个簇由多个IP核构成,这种架构允许达到较高频率,而不会损害电路的操作频率.实验结果表明,该拓扑结构在面积及功耗方面都具有很大优势.解放军电子工程学院刘琪等人提出了一种基于三维网格的星型簇结构的片上网络(3D SCBM-NoC)[184],可以减少路由节点、降低处理节点间的通信代价;通过分析3D SCBM-NoC的拓扑结构,建立了针对星型簇结构的片上网络通信能耗模型.韩国成均馆大学Kim等人提出了一种基于Cmesh和TSV的拓扑结构[91],该结构利用光学互连(OIS)和电子互连(EIS),克服了Cmesh拓扑的局限性,通过降低路由器密度比率提高吞吐量.与传统的3D Mesh片上网络相比,吞吐量提高了19%、功耗减少了48%;与只使用EIS的3D Cmesh片上网络相比,吞吐量提高了70%、功耗减少了28%.

4.4.2 基于路由算法的功耗分析日本会津大学Ahmed等人提出的LA(look-ahead)-XYZ算法可以被分为两步:分配下一个地址和定义新的Next-port[130].优化后的路由算法与传统的三维路由算法相比,在提高系统吞吐量的同时降低了整个系统的通信延迟和功耗.南京大学秦云海等人提出的TPRA(three-dimensional power-adaptive routing algorithm)算法是一种面向功耗的三维自适应路由算法[138],在满足限制规则的情况下引入功耗优化机制,当存在多条可选路径时,路由器会根据网络的功耗状况做出选择.南京大学虞潇等人提出的TFRA(three-dimensional full-adaptive routing algorithm)算法是一种面向功耗的免死锁三维全动态3D NoC路由算法[140],该算法引入了三维空间中6个方向的功耗比较,可以实现3D的全动态路由功能,因此可以大幅度地降低整个系统的功耗.

4.4.3 基于布局算法的功耗分析武汉理工大学郑飞等人提出了基于传递规约无环图的三维布图规划技术3D-TRG,可以根据特定应用优化三维片上网络中模块的布局,从而使功耗更低[74].对图 13(a)中的示例图,根据两两模块之间关系的定义,可以得到如图 13(b)~图 13(d)的3个模块关系图,分别为X方向关系图Gx,y方向关系图Gy,z方向关系图Gz,这3个图的整体就是一个三维布局的表示,记为3D-TRG.基于布图规划技术分别采用了模拟退火、遗传算法和离散粒子群算法对面向特定应用的3D NoC进行了优化,并对3种算法的优化结果进行了对比分析.

|

图 13 三维布图规划技术3D-TRG示意图 Fig.13 Three-Dimensional layout planning technology called 3D-TRG |

航空电子系统综合技术重点实验室葛芬等人提出一种功率和热感知3D NoC映射方法[140],该方法使用遗传算法将IP核映射到3D NoC架构中,以实现最小化功耗和温度偏差的目标,该算法分为4步:① 通过遗传算法产生一个最佳映射集;② 在进入Nigram仿真器的IP核之间输入所确定的通信关系,并设置配置文件;③ 将映射集功耗痕迹作为仿真框架中Hotspot的输入;④ 判断该映射集是否最优.加拿大维多利亚大学Elmiligi等人提出了一种3D NoC功耗分析模型[185],该模型依靠图论概念综合分析静态和动态功耗,更加精确地分析了3D NoC的功耗.

4.4.5 其他形式的功耗分析日本庆应义塾大学张浩等人提出了低功耗技术,只有当晶体管的利用率高于阈值时,才通过切断无线垂直链接的发射机中的偏置电压来停止晶体管工作[64].南京大学虞萧等人提出了3种存储高效的3D NoC架构,分别称为核心、角落和窗户,以实现更好的性能和更低功耗的系统[175].加拿大维多利亚大学Haytham等人引入一种新的3D NoC能耗分析模型[186],该模型依赖于图形和理论概念,组成静态和动态能量以提供更准确的3D NoC功耗评估.

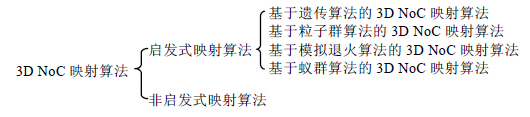

4.5 映射算法综合分析所查到的有关3D NoC映射的研究论文可以看出:大部分3D NoC映射算法是启发式算法,也有一部分非启发式映射算法.3D NoC映射算法的分类如图 14所示.

|

图 14 3D NoC映射算法分类 Fig.14 3D NoC mapping algorithm classification |

启发式映射算法中,基于遗传算法的映射算法包括:基于遗传算法的热感知映射算法[187]、基于逻辑斯蒂函数的自适应遗传算法[188, 189]、基于等级制度的多目标优化遗传映射算法[16, 188]、基于遗传算法的系统优化方

法[190]、热和竞争感知的映射算法[191]、3D Mesh热感知映射算法[192]、功率与热感知映射算法[193]以及采用虚拟IP的3D NoC映射方法[188]等.其中,基于遗传算法的热感知映射算法流程如算法1所示;基于粒子群算法的映射算法包括基于3D-Mesh的CMP片上网络映射方法[194, 195]、基于离散粒子群算法的应用程序映射[196]、使用八面体遍历的集中式3D映射[197]、基于ARPSO的映射算法[198]以及采用仿生优化的拓扑和映射方法[186]等;基于模拟退火算法的映射算法包括针对最小信号TSV的3D NoC映射算法[199]、基于3D Mesh的多播映射方案[5]以及电力输送感知热感知映射框架[200]等,其中,针对最小信号TSV的3D NoC映射算法中层间映射优化算法流程如算法2所示;基于蚁群算法的映射算法包括动态蚁群算法[201]以及面向通信能耗的3D NoC映射算法[202]等.

算法 1 . 基于遗传算法的热感知映射算法.

① 指定层数和层的维数;

② 生成n个随机整数排列阵列;

③ 生成芯片平面布局;

④ 初始化算法,包括功率和通信数据;

⑤ while 未到达最大迭代次数 do

⑥ for 每个解决方案

⑦ 生成布局;

⑧ 计算跳步的通信成本;

⑨ 估计每个PE的温度值;

⑩ 记录峰值温度;

⑪ 评估成本函数;

⑫ end for

⑬ 交叉;

⑭ 变异;

⑮ end while

⑯ 输出最佳解决方案

算法 2 . 层间映射优化算法.

① 随机产生一个层间映射结果M;

② while 初始温度T>最小设定温度Tmin do

③ 随机选择两个IP核;

④ while 所选IP核位于M中的同一层上 do

⑤ 改变两个IP核的位置,获得新的层间映射结果M';

⑥ end while

⑦ if f(M)<f(M')或者exp((f(M')-f(M))/T)>(0-1之间的一个随机数)

then

⑧ 将M'作为当前映射结果;

⑨ end if

⑩ 降低温度;

⑪ end while

⑫ 输出层间映射结果

4.5.2 非启发式映射算法非启发式映射算法包括:快速低能耗映射算法SYMMAP[203, 204]、常规3D NoC热感知算法[205]、应用程序到多电压3D NoC映射算法[206, 207]、功率感知运行时增量映射算法[208]、3种基于ILP的静态热感知映射算法[209]、约束带宽的映射算法[210]、多目标免疫算法[211, 212]、异构3D NoC映射算法[213]以及异构处理机映射算法[214]等.映射算法性能比较见表 3.

| 表 3 映射算法性能比较一览表 Table 3 Performance comparison of different mapping algorithms |

在3D NoC的研究中,还有通信容错、测试、交换技术、服务质量、流量控制、资源网络接口、布局、仿真、定时等研究方向.

4.6.1 通信容错在通信容错方面,Nostrum工程[215]是瑞典皇家理工学院Millberg等人研发的NoC体系结构,它主要研究从物理层到应用层的通信问题.Nostrum通过将每个路由节点连接到另外4个路由节点而形成一个规则的2D Mesh拓扑结构,一个资源(IP核)连接到一个路由节点.该工程基于System C开发了具有图形用户界面(GUI)的仿真环境NNSE,通过GUI配置Nostrum网络的节点数量、拓扑结构、路由策略、流量模式等进行仿真,仿真结果可以采用不同的图形方式显示[216, 217].

4.6.2 测 试3D IC具有比传统的平面IC更高的性能,在3D IC上进行有效的测试架构设计和优化技术可以减少IC的测试代价.3D NoC测试时间优化是一个重要的研究方向,目前已提出了多种不同的测试时间优化方法:合肥工业大学欧阳一鸣等人采用了一种在3D NoC中优化测试时间的技术,在均衡各层IP核测试时间的基础上对IP核进行布局,为各层芯片选择合适的IP核,并利用整数线性规划ILP和随机舍入方法,在总的数据位宽限制下,再次为每层芯片分配相应的TAM数据线宽度,进一步减小各层芯片的测试时间,使得总的测试时间最小[76];桂林电子科技大学尹芝等人针对3D NoC资源内核的测试,采用NoC重用测试访问机制和XYZ路由方式建立功耗模型,并通过云进化算法将IP核的测试数据划分到各TAM上进行并行测试,从而降低了测试时间[75];许川佩等人提出一种功耗限制下测试端口选择优化的方法,从而缩短了测试时间[218].

4.6.3 交换技术路由协议的设计及属性(死锁和活锁)在很大程度上由交换层提供的服务决定,因此,信息交换技术是反映互连网络性能的一个重要因素[26].交换技术影响到数据传输的延迟、功耗、通信架构的面积开销以及死锁等问题.目前的交换技术主要分为电路交换、存储转发技术、虚拟直通技术和虫孔路由技术,其中,后3种交换技术是以数据包的形式转发数据,因此统称为包交换技术[219, 220].文献[221]对几种常见的交换技术进行了比较.文献[222]提出积极的热动态缓存分配方案来限制过热区域周围的路由资源,减少了过热路由区域中包交换的频率.文献[223]分析了3D NoC架构路由算法、虫洞交换架构和MANGO无时钟脉冲NoC中面向连接的服务.

4.6.4 服务质量管理随着芯片网络中数据量的大幅增加,面对用户越来越高的服务要求,必将出现网络中各种业务服务质量难以保证的问题.3D NoC中服务质量管理已成为一个重要的研究方向[224]:2002年,荷兰菲利普实验室Goossens等人开始研究Networks on Silicon和片上互连网络的服务质量,并完成了ASE thereal工程[225];文献[226]对两种服务进行细化,将其划分为4个优先等级;QoS-NoC[227]是面向无连接服务质量保证的应用;Nostrum NoC[215]也是一个面向连接的实现服务质量保证的范例.

4.6.5 流量控制基于信约的路由器到路由器流量控制机制是3D NoC主要采用的链路级流量控制机制:文献[177]基于网络演算分析了基于信约的流量控制机制的性能和最优缓冲区大小,为了对信约的反馈控制行为进行建模,提出了一个抽象的网络服务元素——流量控制器,以定理形式推导出流量控制器和整个系统的服务曲线;为了避免协议和结构性死循环,文献[66]使用泡沫流量控制,泡沫流量控制不依赖于传统的基于VC的避免死锁的机制;文献[228]提出快速的系统级流控,有助于路径发现的研究.

4.6.6 资源网络接口资源网络接口(RNI)是资源(IP核)与网络间的接口,通过RNI接口IP核可以用最小的代价使用网络.同时, IP核和网络资源均可重用.文献[229]提出一种基于统计时分复用(statistical time division multiplex,简称STDM)技术的3D NoC架构,该架构首先在本地子系统中引入STMD控制单元,然后在网络接口设计中增加了计数和等待机制,并对路由节点针对STDM技术进行了优化设计,以增强对STDM的支持,减小总线、网络间的差异.文献[230]提出一种称为Thru Chip接口(thru chip interface,简称TCI)的3D NoC无线互连,使用近场感应耦合以适用于小串音高密度平行通道安排.文献[231]提出一种高效、灵活的分布式的三维叠加DRAM内存接口.

4.6.7 其 他多处理器片上系统对通信带宽的要求与日俱增,结合3D IC和NoC的优点,3D NoC应满足高性能、多功能、缩小芯片面积等设计要求.文献[232]提出一个基于LMS的适应性热预测模型,可以为未来温度估算自适应地调节热RC值.文献[233]介绍了片上存储的逻辑结构、组织结构、电路结构、互连结构,深入分析了片上存储延迟、面积、功耗的建模方法.在总结目前已有的三维片上存储设计的基础上,指出字线划分策略(3D divided wordline,简称3DWL)和位线划分策略(3D divided bitline,简称3DBL)这两种三维存储结构的不足,提出放松工艺约束条件的三维存储结构3DSC(3D subcacheline).文献[18]基于System C环境设计了一个系统级3D NoC仿真器,该仿真器包括处理器模块、存储器模块和互联结构模块,并且支持并行程序在仿真器上的运行,能够在设计初期对加载了应用程序后的系统性能进行仿真.使用该仿真器,可以进行3D NoC的互联结构、路由算法和程序运行性能等方面的探索研究.文献[234]提出3D Mesh中基于路径的多播方法的几种划分方法,效率有所提高.

5 存在的问题与发展趋势 5.1 拓扑结构存在的问题与发展趋势(1) 面向需求的芯片设计是未来一个重要的研究方向,主要研究适合于各种特殊需求的3D NoC拓扑结构,即,实现3D NoC拓扑结构的个性化设计;

(2) 国内外对3D NoC拓扑结构的研究方法主要是计算机模拟仿真,目前尚没有成熟的公开商用的3D NoC仿真平台,关于3D NoC仿真平台的研究是未来的一个研究方向;

(3) 国内外对3D NoC拓扑结构的研究大部分停留在计算机模拟仿真阶段,未来基于各种拓扑结构的3D NoC芯片样片试制是一个重要的研究课题;

(4) 在3D NoC拓扑结构中引入无线技术是一个值得尝试的方向.

5.2 路由存在的问题与发展趋势(1) 目前很少有人研究关于3D Torus的路由算法,而3D Torus比3D Mesh在吞吐量和延迟方面更具优越性,因此,研究适合3D Torus的路由算法是未来的一个研究方向;

(2) 将无关路由与自适应路由算法的优点相结合,研究出具有更好服务质量的路由算法,是今后的一个研究方向;

(3) 随着各种新型3D NoC拓扑结构的提出,研究适合新型拓扑结构的高效路由算法,也将是未来的一个重要研究方向.

5.3 性能评估存在的问题与发展趋势(1) 目前,大部分性能优化算法和容错算法都是针对规则3D NoC拓扑结构提出来的,对于不规则3D NoC架构,对其中可能出现的永久故障问题进行容错以提高片上网络性能,是未来的一个研究方向;

(2) 三维芯片层内的互连线和层间的穿透硅连接的长度、带宽以及信号延时都有很大不同,考虑不同架构层间链路与层内链路的异构性以及信号在线传输延时,通过改进实验仿真程序增加对物理链路的建模,是一个值得尝试的研究方向;

(3) 考虑通信的局部性(即,将通信频繁的簇内节点布置在不同层的相同位置上),然后利用短距离、高带宽的穿透硅连接簇内节点,从而增强通信的局部性,减少消息传输延时、提高系统性能,也是一个需要探索的问题.

5.4 功耗存在的问题与发展趋势(1) 目前,大部分关于功耗的研究都是针对某个方面的功耗优化,对拓扑结构、映射算法、路由算法和布局进行联合优化,是未来的一个研究方向;

(2) 现有的功率控制机制只能动态地运行,当考虑到应用程序的属性时,静态开关机制是非常有利的,静态地关闭目标应用程序的一些链接可以显著地降低功耗,而且没有额外开销.将动态控制和静态控制相结合,是未来的研究方向;

(3) 穿透硅的尺寸、密度、跳变数等因素对功耗会产生很大影响,将3D NoC穿透硅层电路功耗模型与现有的3D NoC功耗模型相结合,提出更为精确的3D NoC功耗模型,是一个值得尝试的研究方向.

5.5 映射存在的问题与发展趋势(1) 3D NoC在增加芯片封装密度和单芯片可集成IP核数的同时,也增加了芯片的能耗密度.因此,低能耗映射在3D NoC的设计过程中显得尤为重要,发热均匀性是未来映射算法设计需要考虑的一个重要因素;

(2) 为了计算在最大延迟模型和流量均衡模型下的参数,现有的映射算法往往设定唯一的路由策略,如XYZ路由算法,这个设定使得算法只适应于各CPU之间通信任务量确定的应用场合,面对突发通信任务较多的应用,一般采用基于动态调整的路由策略.然而,当路由策略采用动态调整时,片上网络路由节点之间的路由路径将由当时的网络拥塞情况决定,此时无法再准确地计算出每个任务的实际延迟时间.因此,如何解决动态路由策略下映射评估模型的优化,是一个需要着重研究的课题;

(3) 目前,大部分3D NoC映射算法都是针对三维规则拓扑结构而提出的,但在实际需求中,面向应用的三维芯片往往具有异构的拓扑结构.因此,个性化3D NoC拓扑结构下低功耗映射算法的研究,是未来3D NoC映射问题的一个研究重点;

(4) 在现阶段研究成果中,3D NoC映射问题的求解大量采用启发式算法,如文中提到的遗传算法、模拟退火算法等都属于这一类.在今后的研究中,可以将不同的优化算法进行组合,例如将模拟退火算法的思想与粒子群算法相结合,以更好地解决3D NoC低功耗映射问题.

6 结束语3D NoC能够有效地解决2D NoC布局受限、难以缩短关键路径长度及减少信号延迟等问题,具有很好的发展前景.本文分析总结了3D NoC的研究现状,对3D NoC解决的关键技术问题进行了分类综述,指出了3D NoC各研究方向存在的问题和发展趋势,对深入开展3D NoC的理论和应用研究都具有重要的意义和参考价值.

| [1] | China Digital Science and Technology Museum. Microelectronics legend-Jack Kilby. 2014. http://amuseum.cdstm.cn/AMuseum/ic/index_02_07_04.html |

| [2] | Liang CD. The influence of hardware architecture on NoC’s performance and research of optimization [MS. Thesis]. Xi’an: Xidian University, 2011 (in Chinese with English abstract). |

| [3] | Wolf W, Jerraya AA, Martin G. Multiprocessor system-on-chip (MPSoC) technology. IEEE Trans. on Computer-Aided Design of Integrated Circuits and Systems, 2008,27(10):1701-1713 . |

| [4] | Bao PL. Research of topology and router for network-on-chip of thousand cores [MS. Thesis]. Xi’an: Xidian University, 2014 (in Chinese with English abstract). |

| [5] | Ding H. Research of multicast-aware mapping for network-on-chip [MS. Thesis]. Xi’an: Xidian University, 2014 (in Chinese with English abstract). |

| [6] | Katabami H, Saito H, Yoneda T. Design of a GALS-NoC using soft-cores on FPGAs. In: Proc. of the 7th IEEE Int’l Symp. on Embedded Multicore Socs (MCSoC). 2013. 31-36 . |

| [7] | Wang CP. Design of high performance NoC interconnect structure based on TSV [MS. Thesis]. Xi’an: Xidian University, 2014 (in Chinese with English abstract). |

| [8] | Magarshack P, Paulin PG. System-on-Chip beyond the nanometer wall. In: Proc. of the 2003 Design Automation Conf. (DAC 2003). Piscataway: IEEE, 2003. 419-424 . |

| [9] | Dally WJ, Towles B. Route packets, not wires: On-Chip interconnection networks. In: Proc. of the 38th Design Automation Conf. (DAC 2001). New York: ACM Press, 2001. 684-689 . |

| [10] | Benini L, De Micheli G. Networks on chips: A new SoC paradigm. IEEE Computer, 2002,35(1):70-78 . |

| [11] | Baidu Encyclopedia. SoC. 2014. http://baike.baidu.com/view/58056.htm |

| [12] | Liu CC, Chen JH, Manohar R, Tiwari S. Mapping system-on chip designs from 2-D to 3-D ICs. In: Proc. of the 2005 IEEE Int’l Symp. on Circuits and Systems (ISCAS2005). Piscataway: IEEE, 2005. 2939-2942 . |

| [13] | Feng GQ, Cai J, Wang SD. Development & applications of through wafer interconnect technology. Electronics & Packaging, 2006, 6(11):15-18 (in Chinese with English abstract). |

| [14] | Lee KM, Lee SJ, Kim DH, Kim K, Kim G, Kim J, Yoo HJ. Networks-on-Chip and networks-in-package for high-performance SoC platforms. In: Proc. of the 2005 IEEE Asian Solid-State Circuits Conf. 2005. 485-488 . |

| [15] | Wang JW, Li L, Zhang Y, Pan HB, He SZ, Zhang R. A hybird hierarchical architecture for 3D multi-cluster NoC. In: Proc. of the 6th Int’l Conf. on Computer Science and Education (ICCSE 2011). 2011. 512-516 . |

| [16] | Wang JW, Li L, Pan HB, He SZ, Zhang R. Latency-Aware mapping for 3D NoC using rank-based multi-objective genetic algorithm. In: Proc. of the Int’l Conf. on ASIC. 2011. 413-416 . |

| [17] | Wang JW, Li L, Yi W, Pan HB, Zhang Y, Hou N, Zhang R. A dynamic ant colony optimization algorithm for 3D NoC mapping. Jisuanji Fuzhu Sheji Yu Tuxingxue Xuebao/Journal of Computer-Aided Design & Computer Graphics, 2011,23(9):1614-1620. |

| [18] | Xie MW, Zhang DL, Li Y. Design of three-dimensional network-on-chip simulator based on System C. Electronic Measurement Technology, 2012,35(6):98-101 (in Chinese with English abstract). |

| [19] | Du GM, Liu X, Song YK, Zhang DL. A temperature gradient based routing algorithm on 3D NoC. In: Proc. of the 2014 Int’l Conf. on Computing, Communication and Networking Technologies (ICCCNT). 2014 . |

| [20] | Zhou L, Wu N, Ge F. 3-D spidergon: 3-D topology of delay optimization for networks-on-chip. Trans. of Nanjing University of Aeronautics & Astronautics, 2011,28(4):372-378. |

| [21] | Chen YO, Hu JH, Ling X. Research on topologic architecture of three-dimensional network on chip. Telecommunications Science, 2009,25(4):39-44 (in Chinese with English abstract). |

| [22] | Chen YO, Hu JH, Ling X. 3D network on chip design based on De Bruijn graph architecture. Journal of Electronicl Science and Technology of China (Natuarl), 2011,40(2):204-209 (in Chinese with English abstract). |

| [23] | Chen YO, Hu JH, Ling X. De Bruijn graph based 3D network on chip architecture design. In: Proc. of the 2009 Int’l Conf. on Communications, Circuits and Systems (ICCCAS 2009). 2009. 986-990 . |

| [24] | Liu YY, Han JG. Study on topology architecture and communication paradigm for network-on-chip [MS. Thesis]. Xi’an: Xidian University, 2009 (in Chinese with English abstract). |

| [25] | Qian Y, Lu ZH, Dou Q, Dou WH. Communication performance analysis of the NoCs in 2D and 3D architectures. Computer Engineering And Science, 2011,33(3):34-40 (in Chinese with English abstract). |

| [26] | Fan JW, Yao FW. Study of 3D network-on-chip [MS. Thesis]. Nanjing: Nangjing University of Posts and Telecommunications, 2011 (in Chinese with English abstract). |

| [27] | Wang H, Fu YZ. A full system simulator and the thermal management research by task scheduling for 3D NoC [MS. Thesis]. Shanghai: Shanghai Jiaotong University, 2011 (in Chinese with English abstract). |

| [28] | Mu J, Fu YZ. Torus architecture research on 3D network-on-chip [MS. Thesis]. Shanghai: Shanghai Jiaotong University, 2010 (in Chinese with English abstract). |

| [29] | Wang LL, Zhang DK, Song ZG. Study of routing algorithms for three dimensional networks-chip. Journal of Chinese Computer Systems, 2014,35(8):1816-1821 (in Chinese with English abstract). |

| [30] | Zhang DK, Song ZG, Wang LL, Huang C. Survey on topologies of three-dimensional network on chip. Journal of Frontiers of Computer Science & Technology, 2015,9(2):129-164 (in Chinese with English abstract). |

| [31] | Duan XM, Zhang DK. A new fault-tolerant routing scheme for N-dimesional mesh. In: Proc. of the 13th Int’l Conf. on Parallel and Distributed Computing, Applications and Technologies, Algorithms and Programming (PDCAT 2012). Beijing, 2012. 642-645 . |

| [32] | Ouyang YM. Research on key issues for testing network on chip [Ph.D. Thesis]. Hefei: Hefei University of Technology, 2013 (in Chinese with English abstract). |

| [33] | Ouyang YM, Wang Y, Liang GH, Huang ZF. Building cluster-based 3D NoC with a weakening network stress method. Journal of Electronic Measurement and Instrument, 2013,27(5):421-428 (in Chinese with English abstract). |

| [34] | Ouyang YM, Yang YZ, Liang GH, Huang ZF. Reuse and fault-tolerant strategies for TSVs of three-dimensional network-on-chip. Journal of Electronic Measurement and Instrument, 2013,27(3):229-235 (in Chinese with English abstract). |

| [35] | Ouyang YM, Zhang YD, Liang GH, Huang ZF. A fault-tolerant design of faults and congestion-aware router in three-dimensional network-on-chip. Acta Electronica Sinica, 2013,41(5):912-917 (in Chinese with English abstract). |

| [36] | Ouyang YM, He M, Liang GH, Liu K, Gao YY. Design of flexible and configurable high-reliability router in 3D Network on-Chip. Journal of Electronic Measurement and Instrument, 2014,28(3):306-313 (in Chinese with English abstract). |

| [37] | Ouyang YM, Zhang YD, Liang GH, Huang ZF, Chang H. Design of fault-tolerant router for 3D NoC based on virtual channel fault granularity partition. Journal of Computer Research and Development, 2014,51(9):1993-2002 (in Chinese with English abstract). |

| [38] | Ouyang YM, Han QQ, Liang GH, Huang ZF, Wang XM. A distributed routing algorithm for reliable communication in vertically partially connected 3D NoC. Journal of Computer-Aided Design & Computer Graphics, 2014,26(3):502-510 (in Chinese with English abstract). |

| [39] | Ouyang J, Xie J, Matthew P, Xie Y. Evaluation of using inductive/capacitive-coupling vertical interconnects in 3D network-on-chip. In: Proc. of the IEEE/ACM Int’l Conf. on Computer-Aided Design, Digest of Technical Papers (ICCAD). 2010. 477-482 . |

| [40] | Paul F, Xie Y, Chang YW, Wang Y. Three-Dimensional integrated circuits (3D IC) floorplan and power/ground network co- synthesis. In: Proc. of the Asia and South Pacific Design Automation Conf. (ASP-DAC). 2010. 169-174 . |

| [41] | Park D, Eachempati S, Das R, Mishra AK, Xie Y, Vijaykrishnan N, Das CR. MIRA: A multi-layered on-chip interconnect router architecture. In: Proc. of the Int’l Symp. on Computer Architecture. 2008. 251-261 . |

| [42] | Sun GY, Wu XX, Xie Y. Exploration of 3D stacked L2 cache design for high performance and efficient thermal control. In: Proc. of the ISLPED 2009. 2009. 295-298 . |

| [43] | Nandakumar VS, Marek-Sadowska M. Low power, high throughput network-on-chip fabric for 3D multicore processors. In: Proc. of the IEEE Int’l Conf. on Computer Design: VLSI in Computers and Processors, 2011. 453-454 . |

| [44] | Ramanujam RS, Lin B. A novel 3D layer-multiplexed on-chip network. In: Proc. of the ANCS 2009: Symp. on Architecture for Networking and Communications Systems. 2009. 123-132 . |

| [45] | Yan S, Lin B. Design of application-specific 3D networks-on-chip architectures. In: Proc. of the 26th IEEE Int’l Conf. on Computer Design (ICCD 2008). 2008. 142-149 . |

| [46] | Ramanujam RS, Lin B. Near-Optimal oblivious routing on three-dimensional mesh networks. In: Proc. of the 26th IEEE Int’l Conf. on Computer Design (ICCD 2008). 2008. 134-141 . |

| [47] | Ramanujam RS, Lin B. A layer-multiplexed 3D on-chip network architecture. IEEE Embedded Systems Letters, 2009,1(2):50-55 . |

| [48] | Canhao XT, Pasi L, Hannu T. Exploring DRAM last level cache for 3D network-on-chip architecture. Advanced Materials Research, 2012,403-408:4009-4018 . |

| [49] | Yin AW, Xu TC, Yang B, Liljeberg P, Tenhunen H. Change function of 2D/3D network-on-chip. In: Proc. of the 11th IEEE Int’l Conf. on Computer and Information Technology (CIT 2011). 2011. 181-188 . |

| [50] | Xu TC, Liljeberg P, Tenhunen H. Optimal number and placement of through silicon vias in 3D network-on-chip. In: Proc. of the 2011 IEEE Symp. on Design and Diagnostics of Electronic Circuits and Systems (DDECS 2011). 2011. 105-110 . |

| [51] | Rahmani AM, Latif K, Liljeberg P, Plosila J, Tenhunen H. Research and practices on 3D networks-on-chip architectures. In: Proc. of the 28th Norchip Conf. (NORCHIP 2010). 2010 . |

| [52] | Rahmani AM, Liljeberg P, Plosila J, Tenhunen H. Exploring a low-cost and power-efficient hybridization technique for 3D NoC-bus hybrid architecture using LastZ-based routing algorithms. Journal of Low Power Electronics, 2012,8(4):403-414 . |

| [53] | Rahmani AM, Liljeberg P, Plosila J, Tenhunen H. LastZ: An ultra optimized 3D networks-on-chip architecture. In: Proc. of the 14th Euromicro Conf. on Digital System Design: Architectures, Methods and Tools (DSD 2011). 2011.173-180 . |

| [54] | Rahmani AM, Vaddina KR, Latif K, Liljeberg P, Plosila J, Tenhunen H. High-Performance and fault-tolerant 3D NoC-bus hybrid architecture using ARB-NET-based adaptive monitoring platform. IEEE Trans. on Computers, 2014,63(3):734-747 . |

| [55] | Rad MRN, Kourdy R, Nasab MR, Poyan M. Improvement the NOC bandwidth and fault tolerant by multipath routing in three- dimensional topologies for multi-media applications. In: Proc. of the 2nd Int’l Conf. on Computer and Automation Engineering. 2010. 497-501 . |

| [56] | Sharifi A, Sabbaghi R, Sarbazi-Azad H. The shuffle-exchange mesh topology for 3D NoCs. In: Proc. of the Int’l Symp. on Parallel Architectures, Algorithms and Networks (I-SPAN). 2008. 275-280 . |

| [57] | Sabbaghi-Nadooshan R, Sarbazi-Azad H. The Kautz mesh: A new topology for SoCs. In: Proc. of the 2008 Int’l SoC Design Conf. 2008. 1300-1303 . |

| [58] | Chao CH, Yin TC, Lin SY, Wu AY. Transport layer assisted routing for non-stationary irregular mesh of thermal-aware 3D network-on-chip systems. In: Proc. of the Int’l System on Chip Conf. 2011. 284-289 . |

| [59] | Huang YR, Pan JH, Lu YC. Thermal-Aware router-sharing architecture for 3D network-on-chip designs. In: Proc. of the IEEE Asia-Pacific Conf. on Circuits and Systems (APCCAS). 2010. 1087-1090 . |

| [60] | Chao CH, Jheng KY, Wang HY, Wu JC, Wu AY. Traffic- and thermal-aware run-time thermal management scheme for 3D NoC systems. In: Proc. of the 4th ACM/IEEE Int’l Symp. on Networks-on-Chip (NOCS 2010). 2010. 223-230 . |

| [61] | Wang Z, Ye YY, Xu J, Wu XW, Zhang W, Liu WC, Mahdi N, Wang X, Wang ZH. Thermal analysis for 3D optical network-on- chip based on a novel low-cost 66 optical router. In: Proc. of the 2012 Optical Interconnects Conf. (OIC 2012). 2012. 110-111 . |

| [62] | Ye YY, Duan L, Xu J, Ouyang J, Hung MK, Xie Y. 3D optical networks-on-chip (NoC) for multiprocessor systems-on-chip (MPSoC). In: Proc. of the 2009 IEEE Int’l Conf. on 3D System Integration (3DIC 2009). 2009 . |

| [63] | Gu HX, Xu J. Design of 3D optical network on chip. In: Proc. of the 2009 Symp. on Photonics and Optoelectronics (SOPO 2009). 2009 . |

| [64] | Zhang H, Matsutani H, Koibuchi M, Amano H. Dynamic power consumption optimization for inductive-coupling based wireless 3D NoCs. Trans. on System LSI Design Methodology, 2014,7:27-36 . |

| [65] | Matsutani H, Koibuchi M, Fujiwara I, Kagami T, Take Y, Kuroda T, Bogdan P, Marculescu R, Amano H. Low-Latency wireless 3D NoCs via randomized shortcut chips. In: Proc. of the Design, Automation and Test in Europe. 2014 . |

| [66] | Take Y, Matsutani H, Sasaki D, Koibuchi M, Kuroda T, Amano H. 3D NoC with inductive-coupling links for building-block SiPs. IEEE Trans. on Computers, 2014,63(3):748-763 . |

| [67] | Matsutani H, Bogdan P, Marculescu R, Take Y, Sasaki D, Zhang H, Koibuchi M, Kuroda T, Amano H. A case for wireless 3D NoCs for CMPs. In: Proc. of the Asia and South Pacific Design Automation Conf. (ASP-DAC). 2013. 23-28 . |

| [68] | Zhang H, Matsutani H, Koibuchi M, Amano H. Dynamic power on/off method for 3D NoCs with wireless inductive-coupling links. In: Proc. of the IEEE Symp. on Low-Power and High-Speed Chips (COOL Chips XVI 2013). 2013 . |

| [69] | de Paulo V, Ababei C. 3D network-on-chip architectures using homogeneous meshes and heterogeneous floorplans. Int’l Journal of Reconfigurable Computing, 2010,(2010):1-12 . |

| [70] | Jheng KY, Chao CH, Wang HY, Wu AY. Traffic-Thermal mutual-coupling co-simulation platform for three-dimensional network-on-chip. In: Proc. of the VLSI Design Automation and Test (VLSI-DAT). 2010. 135-138 . |

| [71] | Jain L. NIRGAM: A simulator for NoC interconnect routing and application modeling. Version 1.1. 2007. |

| [72] | Hemayet H, Mostak A, Abdullah AN, Zerin IT, Mostofa AM. GPNOCSIM—A general purpose simulator for network-on-chip. In: Proc. of the Int’l Conf. on Information and Communication Technology. 2007 . |

| [73] | Pande PP, Grecu C, Jones M, Ivanov A, Saleh R. Performance evaluation and design trade-offs for network-on-chip interconnect architectures. IEEE Trans. on Computers, 2005,54(8):1025-1040 . |

| [74] | Zheng F. Power consumption optimization and simulation of three-dimensional network on chip based on floorplanning [MS. Thesis]. Wuhan: Wuhan University of Technology, 2013 (in Chinese with English abstract). |

| [75] | Yin Z. Research on and implementation of test scheduling for 3D NoC. Electronic Science and Technology, 2014,27(10): 91-94 (in Chinese with English abstract). |

| [76] | Ouyang YM, Liu B, Qi Y. A method to optimize the test time on three-dimensional NoC. Journal of Computer Research and Development, 2010,47(9):332-336 (in Chinese with English abstract). |

| [77] | Stanley FB, Pratim PP. Networks-on-Chip in a three-dimensional environment: A performance evaluation. IEEE Trans. on Computer, 2009,58(1):32-45 . |

| [78] | Kim J, Nicopoulos C, Park D, Das R, Xie Y, Narayanan V, Yousif MS, Das CR. A novel dimensionally-decomposed router for on-chip communication in 3D architectures. ACM Sigarch Computer Architecture News, 2007,35(2):138-149 . |

| [79] | Agyeman MO, Ahmadinia A, Shahrabi A. Low power heterogeneous 3D networks-on-chip architectures. In: Proc. of the 2011 Int’l Conf. on High Performance Computing and Simulation. 2011. 533-538 . |

| [80] | Fantai Z, Ivanov A. 3D multi-processors system on chip design method and performance analysis. In: Proc. of the 2nd IEEE Int’l Conf. on Computer Science and Information Technology (ICCSIT 2009). 2009. 196-199 . |

| [81] | Park D, Eachempati S, Das R, Mishra AK, Xie Y, Vijaykrishnan N, Das CR. MIRA: A multi-layer on chip interconnect router architecture. In: Proc. of the Annual Int’l Symp. on Computer Architecture (ISCA). 2008. 251-261 . |

| [82] | Sun G, Lin SJ, Zhang YY, Su L, Jin DP, Zeng LG. Dual-Link interconnect architecture for 3-D mesh-based network on chip. Journal of Tsinghua University (Science and Technology), 2012,52(5):632-635,641. |

| [83] | Xu Y, Du Y, Zhao B, Zhou XY, Zhang YT, Yang J. A low-radix and low-diameter 3D interconnection network design. In: Proc. of the Int’l Conf. on High Performance Computer Architecture. 2009. 30-42 . |

| [84] | Rahmani AM, Liljeberg P, Plosila J, Tenhunen H. BBVC-3D-NoC: An efficient 3D NoC architecture using bidirectional bisynchronous vertical channels. In: Proc. of the IEEE Annual Symp. on VLSI (ISVLSI 2010). 2010. 452-453 . |

| [85] | Bahmani M, Sheibanyrad A, Petrot F, Dubois F, Durante P. A 3D-NoC router implementation exploiting vertically-partially- connected topologies. In: Proc. of the 2012 IEEE Computer Society Annual Symp. on VLSI (ISVLSI 2012). 2012. 9-14 . |

| [86] | Marcon C, Fernandes R, Cataldo R. Tiny NoC: A 3D mesh topology with router channel optimization for area and latency minimization. In: Proc. of the 27th Int’l Conf. on VLSI Design and the 13th Int’l Conf. on Embedded Systems. 2014. 228-233 . |

| [87] | Mu J. Torus Architecture research on 3D network-on-chip [MS. Thesis]. Shanghai: Shanghai Jiaotong University, 2011 (in Chinese with English abstract). |

| [88] | Duan W, Zhang X, Li M, Zhang C. A compressed 3D-torus architecture for scalable router. In: Proc. of the 4th IEEE Int’l Conf. on Broadband Network and Multimedia Technology (IC-BNMT 2011). 2011. 23-28 . |

| [89] | Wang JH, Gu HX, Yang YT. Cluster mesh: A topology for three-dimensional network-on-chip. IEICE Electronics Express, 2012, 9(15):254-1259 . |

| [90] | Viswanathan N, Paramasivam K, Somasundaram K. Performance analysis of cluster based 3D routing algorithms for NoC. In: Proc. of the 2011 IEEE Recent Advances in Intelligent Computational Systems (RAICS 2011). 2011. 157-162 . |

| [91] | Kim HJ, Seo JT, Han TH. 3CEO: Three dimensional cmesh based electrical-optical router for networks-on-chip. In: Proc. of the 2011 Int’l Conf. on ICT Convergence (ICTC 2011). 2011. 114-119 . |

| [92] | Ebrahimi M, Daneshtalab M, Liljeberg P, Plosila J, Tenhunen H. Cluster-Based topologies for 3D networks-on-chip using advanced inter-layer bus architecture. Journal of Computer & System Sciences, 2013,79(4):475-491 . |

| [93] | Daneshtalab M, Ebrahimi M, Liljeberg P, Plosila J, Tenhunen H. CMIT—A novel cluster-based topology for 3D stacked architectures. In: Proc. of the IEEE 3D System Integration Conf. 2010 . |

| [94] | Viswanathan N, Paramasivam K, Somasundaram K. An optimised 3D topology for on-chip communications. Int’l Journal of Parallel, Emergent and Distributed Systems, 2014,29(4):346-362 . |

| [95] | Li M, Gu HX, Yang YT. A 3D topology based-on partial overlapped clusters for NoC. IEICE Electronics Express, 2014,11(19): 1-6 . |

| [96] | Sharifi A, Nadooshan RS, Azad1 HS. The shuffle-exchange mesh topology for 3D NoCs. In: Proc. of the Int’l Symp. on Parallel Architectures, Algorithms and Networks. Sydney, 2008 . |

| [97] | Chen YO, Hu JH, Ling X. Research on topologic architecture of three-dimensional network on chip. Telecommunications Science, 2009,25(4):39-44. |

| [98] | Chen YO, Hu JH, Ling X. 3D network on chip design based on De Bruijn graph architecture. Dianzi Keji Daxue Xuebao/Journal of the University of Electronic Science and Technology of China, 2011,40(2):204-209. |

| [99] | Chen Y, Hu JH, Ling X. Research on topologic architecture of three dimensional network on chip. Telecommunications Science, 2009,(4):39-44. |

| [100] | Chen Y, Hu JH, Ling X, Huang T. A novel 3D NoC architecture based on De Bruijn graph. Computers & Electrical Engineering, 2012,38(3):801-810 . |

| [101] | Hosseinabady M, Kakoee MR, Mathew J, Pradhan DK. Reliable network-on-chip based on generalized De Bruijn graph. In: Proc. of the IEEE Int’l High Level Design Validation and Test Workshop. 2007 . |

| [102] | He X, You ZQ, Kuang JS. Performance analysis of three dimensional hypercube network topology [MS. Thesis]. China Science and Technology, 2011. |

| [103] | Rahman MMH, Jiang X, Masud SA, Horiguchi S. Network performance of pruned hierarchical torus network. In: Proc. of the 6th IFIP Int’l Conf. on Network and Parallel Computing. 2009. 9-15 . |

| [104] | Ki1 WS, Lee HO, Oh JC. The new torus network design based on 3-dimensional hypercube. In: Proc. of the ICACT 2009. 2009. 615-620. http://xueshu.baidu.com/s?wd=paperuri%3A%287e8ce9de2a6c81246bf8b9f1002c3fc2%29&filter=sc_long_sign&tn= |

| [105] | Liu YY, Han JG. Topology and routing algorithms of hypercube connected double loop interconnect network. Application Research of Computers, 2009,26(3):997-1000 (in Chinese with English abstract). |

| [106] | Liu YY, Han JG. Double-Loop hypercube: A new scalable interconnection network for massively parallel computing. In: Proc. of the ISECS Int’l Colloquium on Computing, Communication, Control and Management (CCCM 2008). 2008. 170-174 . |

| [107] | Kini NG, Kumar MS, Mruthyunjaya HS. A torus embedded hypercube scalable interconnection network for parallel architecture. In: Proc. of the 2009 IEEE Int’l Advance Computing Conf. (IACC). 2009. 858-861 . |

| [108] | Rahman MMH, Horiguchi S. High performance hierarchical torus network under matrix transpose traffic patterns. In: Proc. of the 7th Int’l Symp. on Parallel Architectures, Algorithms and Networks (ISPAN 2004). IEEE, 2004 . |

| [109] | Rahman MMH. Symmetric Tori connected Torus network. In: Proc. of the 12th Int’l Conf. on Computer and Information Technology (ICCIT 2009). 2009. 174-179 . |

| [110] | Yin AW, Xu TC, Liljeberg P, Tenhunen H. Explorations of honeycomb topologies for network-on-chip. In: Proc. of the Int’l Conf. on Network and Parallel Computing. 2009. 73-79 . |

| [111] | Zhou L, Wu N, Ge F. 3-D spidergon: 3-D topology of delay optimization for networks-on-chip. Trans. of Nanjing University of Aeronautics & Astronautics, 2011,28(4):372-378. |

| [112] | Wang H, Wang CS. 3D octagon double ring topology for the network-on-chip. China Integrated Circuit, 2011,(3):27-30,65. |

| [113] | Matsutani H, Koibuchi M, Amano H. Tightly-Coupled multi-layer topologies for 3D NoCs. In: Proc. of the Int’l Conf. on Parallel Processing. Xi’an, 2007 . |

| [114] | Seiculescu C, Murali S, Benini L, Micheli GD. SunFloor 3D: A tool for networks on chip topology synthesis for 3D systems on chips. In: Proc. of the Design, Automation & Test in Europe Conf. & Exhibition. 2009. 9-14 . |

| [115] | Weldezion AY, Lu Z, Weerasekera R, Tenhunen H. 3-D memory organization and performance analysis for multi-processor network-on-chip architecture. In: Proc. of the 2009 IEEE Int’l Conf. on 3D System Integration (3DIC 2009). 2009 . |

| [116] | Li F, Nicopoulos C, Richardson T, Xie Y, Narayanan V, Kandemir M. Design and management of 3D chip multiprocessors using network-in-memory. In: Proc. of the 33rd Int’l Symp. on Computer Architecture (ISCA 2006). 2006. 130-141 . |

| [117] | Jang WY, Pan DZ. Chemical-Mechanical polishing-aware application-specific 3D NoC design. IEEE Trans. on Computer-Aided Design of Integrated Circuits and Systems, 2013,32(6):940-951 . |

| [118] | Ge F, Wu N. Power-Aware topology generation based on clustering for application-specific network on chip. Lecture Notes in Electrical Engineering, 2013,170(1):135-149 . |

| [119] | Morris RW, Kodi AK, Louri A, Whaley RD. Three-Dimensional stacked nanophotonic network-on-chip architecture with minimal reconfiguration. IEEE Trans. on Computers, 2014,63(1):243-255 . |

| [120] | Latif K, Rahmani AM, Nigussie E, Tenhunen H, Seceleanu T. A novel topology-independent router architecture to enhance reliability and performance of networks-on-chip. In: Proc. of the 2011 IEEE Int’l Symp. on Defect and Fault Tolerance in VLSI and Nanotechnology Systems (DFT 2011). 2011. 454-462 . |

| [121] | Camacho J, Flich J. HPC-Mesh: A homogeneous parallel concentrated mesh for fault-tolerance and energy savings. In: Proc. of the 7th ACM/IEEE Symp. on Architectures for Networking and Communications Systems. 2011. 69-80 . |

| [122] | Zheng YX, Kan PP, Chen LB, Hsieh KY, Cheng BC, Li KSM. Fault tolerant application-specific NoC topology synthesis for three-dimensional integrated circuits. In: Proc. of the IEEE Int’l SOC Conf. (SOCC 2011). 2011. 296-301 . |

| [123] | Hsieh KY, Cheng BC, Gu RT, Li KSM. Fault-Tolerant mesh for 3D network on chip. In: Proc. of the Int’l Microsystems, Packing, Assembly and Circuits Technology Conf. 2011.202-205 . |

| [124] | Zia A, Kannan S, Rose G, Chao HJ. Highly-Scalable 3D Clos NoC for many-core CMPs. In: Proc. of the 8th IEEE Int’l NEWCAS Conf. (NEWCAS 2010). 2010.229-232 . |

| [125] | Pasricha S. Exploring serial vertical interconnects for 3D ICs. In: Proc. of the Design Automation Conf. 2009. 581-586. http://xueshu.baidu.com/s?wd=paperuri%3A%287e8ce9de2a6c81246bf8b9f1002c3fc2%29&filter=sc_long_sign&tn=SE_xueshusource_2kduw22v&sc_vurl=http%3A%2F%2Fieeexplore.ieee.org%2Fxpls%2Fabs_all.jsp%3Farnumber%3D4810028&ie=utf-8 |

| [126] | Pei SW, Wang XY. Shuttle: A novel topology model for 3D NoC. Journal of Convergence Information Technology, 2012, 7(19):147-154 . |

| [127] | Bose A, Ghosal P, Mohanty SP. A low latency scalable 3D NoC using BFT topology with table based uniform routing. In: Proc. of the 2014 IEEE Computer Society Annual Symp. on VLSI. 2014. 136-141 . |

| [128] | Matos D, Reinbrecht C, Motta T, Susin A. A power-efficient hierarchical network-on-chip topology for stacked 3D ICs. In: Proc. of the 2013 IFIP/IEEE 21st Int’l Conf. on Very Large Scale Integration (VLSI-SoC). 2013. 308-313 . |

| [129] | Khan MA, Ansari AQ. Quadrant-Based XYZ dimension order routing algorithm for 3-D asymmetric torus networ-on-chip. In: Proc. of the Networks and Computer Communications (ETNCC). 2011. 121-124 . |

| [130] | Ahmed AB, Abdallah AB. Low-Overhead routing algorithm for 3D network-on-chip. In: Proc. of the 3rd Int’l Conf. on Networking and Computing (ICNC 2012). 2012.23-32 . |

| [131] | Bala D, You C. Volumetric degenerative routing for 3D network-on-chip. In: Proc. of the 2012 IEEE Int’l Conf. on Wireless Information Technology and Systems (ICWITS 2012).2012 . |

| [132] | Sun G, Chang CW, Lin B, Zeng L. An oblivious routing algorithm for 3D mesh networks to achieve a new worst-case throughput bound. IEEE Embedded Systems Letters, 2012,4(4):98-101 . |

| [133] | Ahmed M, Kumar R. Parameterized path-based, randomized, oblivious, minimal routing in 3D mesh NoC. In: Proc. of the 10th IEEE Region Conf. 2012. 1-6 . |

| [134] | Feng CC, Zhang MX, Li JW, Jiang J, Lu ZH, Jantsch A. A low-overhead fault-aware deflection routing algorithm for 3D network-on-chip. In: Proc. of the 2011 IEEE Computer Society Annual Symp. on VLSI (ISVLSI 2011). 2011. 19-24 . |

| [135] | Pasricha S, Zou Y. A low overhead fault tolerant routing scheme for 3D networks-on-chip. In: Proc. of the 12th Int’l Symp. on Quality Electronic Design (ISQED 2011). 2011. 1-8 . |

| [136] | Akbari S, Shafiee A, Fathy M, Berangi R. AFRA: A low cost high performance reliable routing for 3D mesh NoCs. In: Proc. of the Design, Automation and Test in Europe Conf. and Exhibition (DATE 2012). 2012. 332-337 . |

| [137] | Zhu MY, Lee JH, Choi KY. An adaptive routing algorithm for 3D mesh NoC with limited vertical bandwidth. In: Proc. of the 20th IFIP/IEEE Int’l Conf. on Very Large Scale Integration (VLSI-SoC 2012). 2012. 18-23 . |

| [138] | Qin YH, Li L. Research on 3D NoC power adaptive routing methodology [Ph.D. Thesis]. Nanjing: Nanjing University, 2012 (in Chinese with English abstract). |

| [139] | Lin SY, Yin TC, Wang HY, Wu AY. Traffic- and thermal-aware routing for throttled three-dimensional network-on-chip systems. In: Proc. of the 2011 Int’l Symp. on VLSI Design, Automation and Test (VLSI-DAT 2011). 2011. 1-4 . |

| [140] | Yu X, Li L, Zhang YA, Pan HB, Wang JW, Han P. A power-aware dead lock avoid three-dimensional full-adaptive routing algorithm for 3D NoC. Tien Tzu Hsueh Pao/Acta Electronica Sinica, 2013,41(2):329-334. |

| [141] | Rusu C, Anghel L, Avresky D. RILM: Reconfigurable inter-layer routing mechanism for 3D multi-layer networks-on-chip. In: Proc. of the 16th IEEE Int’l On-Line Testing Symp. (IOLTS 2010). 2010. 121-126 . |

| [142] | Rusu C, Anghel L, Avresky D. Adaptive inter-layer message routing in 3D networks-on-chip. Microprocessors and Microsystems, 2011,35(7):613-631 . |

| [143] | Ying H, Jaiswal A, Hofmann K. Deadlock-Free routing algorithms for 3-dimension networks-on-chip with reduced vertical channel density topologies. In: Proc. of the 2012 Int’l Conf. on High Performance Computing and Simulation (HPCS 2012). 2012. 268-274 . |

| [144] | Dubois F, Sheibanyrad A, Petrot F, Bahmani M. Elevator-First: A deadlock-free distributed routing algorithm for vertically partially connected 3D-NoCs. IEEE Trans. on Computers, 2013,62(3):609-615 . |

| [145] | Wang K, Wang CS, Gu HX. Quality of service routing algorithm in the torus-based network on chip. In: Proc. of the 8th IEEE Int’l Conf. on ASIC (ASICON 2009). 2009. 952-954 . |

| [146] | Nakhjavani R, Shahabi A, Safari S, Navabi Z. A novel graceful degradable routing algorithm for 3D on-chip networks. In: Proc. of the 2012 Interconnection Network Architecture: On-Chip, Multi-Chip Workshop (INA-OCMC 2012). 2012. 17-20 . |

| [147] | Dahir N, Al-Dujaily R, Yakovlev A, Missailidis P, Mak T. Deadlock-Free and plane-balanced adaptive routing for 3D networks-on-chip. In: Proc. of the 5th Int’l Workshop on Network on Chip Architectures (NoCArc 2012) and Conjunction with the 45th Annual IEEE/ACM Int’l Symp. on Microarchitecture (MICRO 2012). 2012. 31-36 . |

| [148] | Ebrahimi M, Xin C, Daneshtalab M, Plosila J, Liljeberg P, Tenhunen H. DyXYZ: Fully adaptive routing algorithm for 3D NoCs. In: Proc. of the 21st Euromicro Int’l Conf. on Parallel, Distributed, and Network-Based Processing. 2013. 499-503 . |

| [149] | Lee JH, Lee DW, Kim SW, Choi K. Deflection routing in 3D network-on-chip with TSV serialization. In: Proc. of the Asia and South Pacific Design Automation Conf. (ASP-DAC). 2013. 29-34 . |

| [150] | Lee JH, Choi K. A deadlock-free routing algorithm requiring no virtual channel on 3D-NoCs with partial vertical connections. In: Proc. of the 7th IEEE/ACM Int’l Symp. on Networks-on-Chip (NoCS 2013). 2013 . |

| [151] | Chen KC, Lin SY, Hung HS, Wu AA. Topology-Aware adaptive routing for nonstationary irregular mesh in throttled 3D NoC systems. IEEE Trans. on Parallel and Distributed Systems, 2013,24(10):2109-2120 . |

| [152] | Chen KC, Kuo CC, Hung HS, Wu AYA. Traffic- and thermal-aware adaptive beltway routing for three dimensional network-on- chip systems. In: Proc. of the IEEE Int’l Symp. on Circuits and Systems. 2013. 1660-1663 . |

| [153] | Ebrahimi M, Daneshtalab M, Plosila J. Fault-Tolerant routing algorithm for 3D NoC using Hamiltonian path strategy. In: Proc. of the Design, Automation and Test in Europe (DATE). 2013. 1601-1604 . |

| [154] | Jiang X, Watanabe T. A novel fully adaptive fault-tolerant routing algorithm for 3D network-on-chip. In: Proc. of the 10th IEEE Region Conf. 2013. 1-4 . |

| [155] | Ying HY, Hofmann K, Hollstein T. Dynamic quadrant partitioning adaptive routing algorithm for irregular reduced vertical link density topology 3-dimensional network-on-chips. In: Proc. of the 2014 Int’l Conf. on High Performance Computing and Simulation. 2014. 516-522 . |

| [156] | Chang WC, Tseng HW, Kuo CF. A traffic-balanced routing scheme for heat balance in 3D networks-on-chip. In: Proc. of the ACM Symp. on Applied Computing. 2014. 1437-1442 . |

| [157] | Kumar M, Laxmi V, Gaur M, Daneshtalab M, Ko SB, Zwolinski M. Highly adaptive and congestion-aware routing for 3D NoCs. In: Proc. of the ACM Great Lakes Symp. on VLSI (GLSVLSI). 2014. 97-98 . |

| [158] | Meena NK, Kapoor HK, Chakraborty S. A new recursive partitioning multicast routing algorithm for 3D network-on-chip. In: Proc. of the 18th Int’l Symp. on VLSI Design and Test. 2014 . |

| [159] | Somasundaram K, Plosila J, Viswanathan N. Deadlock free routing algorithm for minimizing congestion in a Hamiltonian connected recursive 3D-NoCs. Microelectronics Journal, 2014,45(8):989-1000 . |

| [160] | Tsai WC, Weng YY, Wei CJ, Chen SJ, Hu YH. 3D bidirectional-channel routing algorithm for network-based many-core embedded systems. Lecture Notes in Electrical Engineering, 2014,260:301-309 . |

| [161] | Ouyang YM, Han QQ, Liang HG, Huang ZF, Wang XM. A distributed routing algorithm for reliable communication in vertically partially connected 3D NoC. Jisuanji Fuzhu Sheji Yu Tuxingxue Xuebao/Journal of Computer-Aided Design and Computer Graphics, 2014,26(3):502-510 (in Chinese with English abstract). |

| [162] | Ahmed AB, Abdallah AB. Graceful deadlock-free fault-tolerant routing algorithm for 3D network-on-chip architectures. Journal of Parallel & Distributed Computing, 2014,74(4):2229-2240 . |

| [163] | Hu ZK, Chen J. A hybrid multicast routing algorithm based on hierarchical NoCs. Journal of Harbin Engineering University, 2013,34(10):1327-1333 (in Chinese with English abstract). |

| [164] | Zhang YY, Hu JH. A DFTR router architecture for 3D network on chip. In: Proc. of the 3rd IEEE Int’l Conf. on Computer Science and Information Technology (ICCSIT 2010). 2010. 337-342 . |

| [165] | Chen KC, Chao CH, Lin SY, Hung HS, Wu AY. Transport-Layer assisted vertical traffic balanced routing for thermal-aware three-dimensional network-on-chip systems. In: Proc. of the 2012 Int’l Symp. on VLSI Design, Automation and Test (VLSI-DAT 2012). 2012. 1-4 . |

| [166] | Salas M, Pasricha S. The roce-bush router: A case for routing-centric dimensional decomposition for low-latency 3D NoC routers. In: Proc. of the 10th ACM Int’l Conf. on Hardware/Software-Codesign and System Synthesis, Co-located with ESWEEK (CODES+ ISSS 2012). 2012. 171-180 . |

| [167] | Al-Dujaily R, Dahir N, Mak T, Xia F, Yakovlev A. Dynamic programming-based runtime thermal management (DPRTM): An online thermal control strategy for 3D-NoC systems. ACM Trans. on Design Automation of Electronic Systems, 2013,19(1): 992-999 . |

| [168] | Ghidini Y, Webber T, Moreno E, Quadros I, Fagundes R, Marcon C. Topological impact on latency and throughput: 2D versus 3D NoC comparison. In: Proc. of the 25th Symp. on Integrated Circuits and Systems Design (SBCCI 2012). 2012 . |

| [169] | Moosavi SR, Rahmani AM, Liljeberg P, Plosila J, Tenhunen H. Enhancing performance of 3D interconnection networks using efficient multicast communication protocol. In: Proc. of the 21st Euromicro Int’l Conf. on Parallel, Distributed, and Network- Based Processing. 2013. 294-301 . |

| [170] | Pasca V, Rehman SU, Anghel L, Benabdenbi M. Efficient link-level error resilience in 3D NoCs. In: Proc. of the 15th IEEE Int’l Symp. on Design and Diagnostics of Electronic Circuits and Systems. 2012. 127-132 . |

| [171] | Zjajo A, van de Meerendonk N, Van Leuken R. Dynamic thermal estimation methodology for high-performance 3-D MPSoC. IEEE Trans. on Very Large Scale Integration (VLSI) Systems, 2014,22(9):1920-1933 . |

| [172] | Zhang Y, Li L, Lu ZH, Jantsch A, Fu YX, Gao ML. Performance and network power evaluation of tightly mixed SRAM NUCA for 3D multi-core network on chips. In: Proc. of the IEEE Int’l Symp. on Circuits and Systems. 2014. 1961-1964 . |

| [173] | Mu J, Fu ZY, Liu T. Performance evaluation for the 3D architectures in network on chip. Information Technology, 2010,(5):70-73 (in Chinese with English abstract). |

| [174] | He X, You ZQ, Kuang JS. Performance analysis for 3D hypercube network on chip. 2011 (in Chinese with English abstract). http://www.paper.edu.cn/releasepaper/content/201112-185 |

| [175] | Yu X, Li L, Zhang Y, Pan HB. Performance and power consumption analysis of memory efficient 3D network-on-chip architecture. In: Proc. of the IEEE Int’l Conf. on Control and Automation (ICCA). 2013. 340-344 . |

| [176] | Morris R, Kodi A, Louri A. Evaluating the scalability and performance of 3D stacked reconfigurable nanophotonic interconnects. In: Proc. of the Int’l Workshop on System Level Interconnect Prediction. 2013 . |

| [177] | Qian Y. Calculus models and performance analysis for networks-on-chip [Ph.D. Thesis]. Changsha: Science and Technology University, 2010 (in Chinese with English abstract). |

| [178] | Zhang YY, Lin SJ, Su L, Jin DP, Zeng LG. Performance evaluation of turus and mesh in 3D network-on-chip. Jounal of Tsinghua University (Science and Technology), 2011,51(12):1777-1781 (in Chinese with English abstract). |

| [179] | He X. The implementation and performance analysis of hypercube in three dimensions network on chip [MS. Thesis]. Changsha: Hu’nan University, 2012 (in Chinese with English abstract). |

| [180] | Jiang P. TSV power model and 3D NoC power consumption analysis [MS. Thesis]. Xi’an: Xidian University, 2012 (in Chinese with English abstract). |

| [181] | Ye TT, Benini L, De Micheli G. Packetized on-chip interconnect communication analysis for MPSoC. In: Proc. of the Design, Automation and Test in Europe Conf. and Exhibition. 2003. 344-349 . |

| [182] | Eisley N, Peh LS. High level power analysis for on-chip networks. In: Proc. of the 2004 Int’l Conf. on Compilers, Architecture and Synthesis for Embedded Systems. ACM Press, 2004 . |

| [183] | Huang G. The research and application of power model for interconnection network in MPSoC [MS. Thesis]. Xi’an: Xidian University, 2011 (in Chinese with English abstract). |

| [184] | Liu Q, Li DS. Communication energy-aware research of star cluster NoC. Application Research of Computers, 2012,29(6): 2176-2179 (in Chinese with English abstract). |

| [185] | Ge F, Feng G, Yu S, Wu N. Power- and thermal-aware mapping for 3D network-on-chip. Information Technology Journal, 2013, 12(23):7297-7304 . |

| [186] | Elmiligi H, El-Kharashi MW, Gebali F. Power consumption of 3D networks-on-chips: Modeling and optimization. Microprocessors and Microsystems, 2013,37(6-7):530-543 . |

| [187] | Addo-Quaye C. Thermal-Aware mapping and placement for 3-D NoC designs. In: Proc. of the IEEE Int’l SOC Conf. 2005. 25-28 . |

| [188] | Wang JW. Research of key issue on three dimensional network on chip [Ph.D. Thesis]. Nanjing: Nanjing University, 2012 (in Chinese with English abstract). |

| [189] | Wang JW, Li L, Wang ZF, Zhang R, Zhang Y. Energy-Efficient mapping for 3D NoC usinglogistic function based adaptive geneticalgorithms. Chinese Journal of Electronics, 2014,23(2):254-262. |

| [190] | Ying HY, Heid K, Hollstein T, Hofmann K. A genetic algorithm based optimization method for low vertical link density 3-dimensional networks-on-chip many core systems. In: Proc. of the NORCHIP 2012. 2012 . |

| [191] | Zhang BX, Gu HX, Yang YT, Wang K, Wang ZY. Thermal and competition aware mapping for 3D network-on-chip. IEICE Electronics Express, 2012,9(19):1510-1515 . |

| [192] | Feng G, Ge F, Yu S, Wu N. A Thermal-aware mapping algorithm for 3D mesh network-on-chip architecture. In: Proc. of the 10th IEEE Int’l Conf. on ASIC. 2013 . |

| [193] | Ge F, Feng G, Yu S, Wu N. Power- and thermal-aware mapping for 3D network-on-chip. Information Technology Journal, 2013, 12(23):7297-7304 . |

| [194] | Zhang Z. Research of mapping methods for 3D-MESH-oriented CMP networks on chip [MS. Thesis]. Guangzhou: Guangdong University of Technology, 2012 (in Chinese with English abstract). |

| [195] | Zhang W, Zhang Z, Liu YJ. Improved particle swarm optimization algorithm based mapping algorithm for 3D-mesh CMP. Application Research of Computers, 2013,30(5):1345-1348 (in Chinese with English abstract). |

| [196] | Sahu PK, Shah T, Manna K, Chattopadhyay S. Application mapping onto mesh-based network-on-chip using discrete particle swarm optimization. IEEE Trans. on Very Large Scale Integration (VLSI) Systems, 2014,22(2):300-312 . |

| [197] | Bhardwaj K, Mane PS. C3Map and ARPSO based mapping algorithms for energy-efficientregular 3-D NoC architectures. In: Proc. of the Technical Papers of 2014 Int’l Symp. on VLSI Design, Automation and Test. 2014 . |

| [198] | Riget J, Vesterstrom J. A diversity-guided particle swarm optimizer the ARPSO. Technical Report, Aarhus: Department of Computer Science, University of Aarhus, 2002. |

| [199] | Ding H, Gu HX, Yang YT, Fan DR. 3D networks-on-chip mapping targeting minimum signal TSVs. IEICE Electronics Express, 2013,10(18):1-6. |

| [200] | Kapadia N, Pasricha S. PRATHAM: A power delivery-aware and thermal-aware mapping framework for parallel embedded applications on 3D MPSoCs. In: Proc. of the 32nd IEEE Int’l Conf. on Computer Design (ICCD 2014). 2014. 525-528 . |

| [201] | Wang JW, Li L, Yi W, Pan HB, Zhang YH, Hou N, Zhang R. A dynamic ant colony optimization algorithm for 3D NoC mapping. Journal of Computer-Aided Design & Computer Graphics, 2011,23(9):1614-1620 (in Chinese with English abstract). |

| [202] | Li DS, Liu Q. Researchon mapping 3D network on chip for communication energy-aware. Semiconductor Technology, 2012,37(7): 504-507 (in Chinese with English abstract). |

| [203] | Liu YH. Research on key technologies of mapping and router in network-on-chip [Ph.D. Thesis]. Shanghai: East China Normal University, 2013 (in Chinese with English abstract). |

| [204] | Liu YH, Ruan Y, Lai ZS. New heuristic algorithms for low-energy mapping and routing in 3D NoC. Int’l Journal of Computer Applications in Technology, 2013,47(1):1-13 . |

| [205] | Arjomand M, Sarbazi-Azad H. Voltage-Frequency planning for thermal-aware, low-power design of regular 3-D NoCs. In: Proc. of the 23rd Int’l Conf. on VLSI Design. 2010. 57-62 . |

| [206] | Siozios K, Anagnostopoulos I, Soudris D. Multiple VDD on 3D NoC architectures. In: Proc. of the Electronics, Circuits, and Systems (ICECS). 2010. 831-834 . |

| [207] | Siozios K, Anagnostopoulos I, Soudris D. A high-level mapping algorithm targeting 3D NoC architectures with multiple VDD. In: Proc. of the 2010 IEEE Annual Symp. on VLSI. 2010.444-445 . |

| [208] | Wang XH, Palesi M, Yang M, Jiang YT, Huang MC, Liu P. Power-Aware run-time incremental mapping for 3-D networks-on-chip. In: Proc. of the IFIP Int’l Federation for Information Processing 2011. 2011. 232-247 . |

| [209] | Hamedani PK, Hessabi S, Sarbazi-Azad1 H, Jerger NE. Explorationof temperature constraints for thermal aware mapping of 3D networks on chip. In: Proc. of the 20th Euromicro Int’l Conf. on Parallel. 2012. 499-506 . |

| [210] | Eskandari A, Khademzadeh A, Bagherzadeh N, Janidarmian M. Quality of service optimization for network-on-chip using bandwidth- constraint mapping algorithm. In: Proc. of the 21st Euromicro Int’l Conf. on Parallel. 2013. 504-508 . |

| [211] | Sepúlveda J, Gogniat G, Pires R, Wang C, Strum M. An evolutive approach for designing thermal and performance-aware heterogeneous 3D-NoCs. In: Proc. of the 26th Symp. on Integrated Circuits and Systems Design. 2013. 6 . |

| [212] | Johanna S, Gogniat G, Sepúlveda DM, Pires R, Chau WJ, Strum M. 3DMIA: A multi-objective artificial immune algorithm for 3D-MPSoC multi-application 3D-NoC mapping. In: Proc. of the 2013 Genetic and Evolutionary Computation Conf. New York: ACM, 2013. 167-168 . |

| [213] | Agyeman MO, Ahmadinia A. Optimised application specific architecture generation and mapping approach for heterogeneous 3D networks-on-chip. In: Proc. of the 16th IEEE Int’l Conf. on Computational Science and Engineering. 2013.794-801 . |

| [214] | Akturk I, Ozturk O. ILP-Based communication reduction for heterogeneous 3D network-on-chips. In: Proc. of the 21st Euromicro Int’l Conf. on Parallel, Distributed and Network-Based Processing. 2013. 514-518 . |

| [215] | Millberg M, Nilsson E, Thid R, Kumar S, Jantsch A. The Nostrum backbone—A communication protocol stack for networks on chip. In: Proc. of the VLSI Design Conf. Mumbai. 2004. 693-696 . |

| [216] | Millberg M, Jantsch A, Lu Z, Thid R, Nilsson E. NNSE: Nostrum network-on-chip simulation environment. In: Proc. of the Swedish System-on-Chip Conf. (SSoCC 2003). 2005. 1-4. |

| [217] | Bjureus P, Millberg M, Jantsch A. FPGA resource and timing estimation from Matlab execution traces. In: Proc. of the 10th Int’l Symp. on Hardware/Software Codesign. 2002. 31-36. |

| [218] | Xu CP, Yao YX. Optimized test ports selecting method on 3D-NoC. Application Research of Computers, 2015,32(3):1-5 (in Chinese with English abstract). |

| [219] | Xu X. Research on routing algorithm and mapping algorithm in network on chip [MS. Thesis]. Xi’an: Xidian University, 2010 (in Chinese with English abstract). |

| [220] | Dong SZ. The design and research of routing algorithm and simulation model on network on chips [MS. Thesis]. Hefei: Hefei University of Technology, 2009 (in Chinese with English abstract). |

| [221] | Yang YZ. Research of the fault-tolerant methods on TSVs and buffers of three-dimensional network-on-chip [MS. Thesis]. Hefei: Hefei University of Technology, 2013 (in Chinese with English abstract). |

| [222] | Lee YS, Hsin HK, Chen KC, Chang EJ, Wu AYA. Thermal-Aware dynamic buffer allocation for proactive routing algorithm on 3D network-on-chip systems. In: Proc. of the Technical Papers of 2014 Int’l Symp. on VLSI Design, Automation and Test. 2014 . |

| [223] | Ramani S, Sundararajan J. A case study on NoC router architecture for optimizing the latency. In: Proc. of the Int’l Conf. on Advanced Computing and Communication Systems (ICACCS). 2013. 1-4 . |

| [224] | Wang F. Research on QoS assurance mechanism based on 3D-mesh [MS. Thesis]. Chengdu: University of Electronic Science and Technology of China, 2012 (in Chinese with English abstract). |

| [225] | Goossens K, Dielissen J, Radulescu A. Ethereal network on chip: Concepts, architectures and implementations. In: Proc. of the IEEE Design & Test of Computers. 2005. 414-421 . |

| [226] | Chiu GM. The ODD-even turn model for adaptive routing. IEEE Trans. on Parallel and Distributed Systems, 2000,11(7):729-738 . |

| [227] | Bolotin E, Cidon I, Ran G, Kolodny A. QNoC: QoS architecture and design process for network on chip. Journal of Systems Architecture, 2004,50(2-3):105-128 . |

| [228] | Priyadarshi S, Hu JC, Choi WH, Melamed S, Chen X, Davis WR. Pathfinder 3D: A flow for system-level design space exploration. In: Proc. of the 2011 IEEE Int’l 3D Systems Integration Conf. 2011. 1-8 . |

| [229] | Wang JW, Li L, Pan HB, Li W, Zhang R. 3D NoC based on statistical time division multiplex. Journal of Electronics & Information Technology, 2012,10(34):2501-2507 (in Chinese with English abstract). |

| [230] | Kuroda T. ThruChip interface (TCI) for 3D networks on chip. In: Proc. of the 19th IEEE/IFIP Int’l Conf. on VLSI and System-on-Chip. 2011. 238-241 . |

| [231] | Loi I, Benini L. An efficient distributed memory interface for many-core platform with 3D stacked DRAM. In: Proc. of the Design, Automation and Test in Europe. 2010. 99-104 . |

| [232] | Chen KC, Li HT, Wu AY. LMS-Based adaptive temperature prediction scheme for proactive thermal-aware three-dimensional network-on-chip systems. In: Proc. of the Technical Papers of 2014 Int’l Symp. on VLSI Design, Automation and Test. 2014 . |

| [233] | Wang Y. Research on three dimensional memory architecture in multi-core processors [MS. Thesis]. Changsha: National University of Defense Technology, 2011 (in Chinese with English abstract). |

| [234] | Ebrahimi M, Daneshtalab M, Liljeberg P, Plosila J, Flich J, Tenhunen H. Path-Based partitioning methods for 3D networks-on-chip with minimal adaptive routing. IEEE Trans. on Computers, 2014,63(3):718-733 . |

| [2] | 梁春东.硬件架构对片上网络性能影响及优化策略研究[硕士学位论文].西安:西安电子科技大学,2011. |

| [4] | 鲍培蕾.面向千核片上网络拓扑结构和路由器的研究[硕士学位论文].西安:西安电子科技大学,2014. |

| [5] | 丁慧.片上网络多播映射研究[硕士学位论文].西安:西安电子科技大学,2014. |

| [7] | 王昌鹏.基于TSV的NoC高性能互连结构设计[硕士学位论文].西安:西安电子科技大学,2014. |

| [13] | 封国强,蔡坚,王水弟.硅通孔互连技术的开发与应用.电子与封装,2006,6(11):15-18. |

| [18] | 谢门旺,张多利,李垚.基于SystemC的三维片上网络仿真器设计.电子测量技术,2012,35(6):98-101. |

| [21] | 陈亦欧,胡剑浩,凌翔.三维片上网络拓扑研究.电信科学,2009,25(4):39-44. |

| [22] | 陈亦欧,胡剑浩,凌翔.建立在De Bruijn图架构上的三维片上网络设计.电子科技大学学报(自然科学版),2011,40(2):204-209. |

| [24] | 刘有耀,韩俊刚.片上网络拓扑结构与通信方法研究[硕士学位论文].西安:西安电子科技大学,2009. |

| [25] | 钱悦,鲁中海,窦强,窦文华.片上网络二维和三维结构的通信性能分析.计算机工程与科学,2011,33(3):34-40. |

| [26] | 范敬雯,姚放吾.三维片上网络的研究[硕士学位论文].南京:南京邮电大学,2011. |

| [27] | 汪涵,付宇卓.3D-Noc全系统仿真器搭建和基于任务调度的温度管理研究[硕士学位论文].上海:上海交通大学,2011. |

| [28] | 穆静,付宇卓.Torus拓扑结构的三维片上网络研究[硕士学位论文].上海:上海交通大学,2010. |

| [29] | 王莲莲,张大坤,宋国治.三维片上网络路由算法的研究.小型微型计算机系统,2014,35(8):1816-1821. |

| [30] | 张大坤,宋国治,王莲莲,黄翠.三维片上网络拓扑结构研究综述.计算机科学与探索,2015,9(2):129-164. |

| [32] | 欧阳一鸣.片上网络测试关键问题研究[博士学位论文].合肥:合肥工业大学,2013. |

| [33] | 欧阳一鸣,王宇,梁华国,黄正峰.簇式三维片上网络通信压力弱化策略.电子测量与仪器学报,2013,27(5):421-428. |

| [34] | 欧阳一鸣,杨懿泽,梁华国,黄正峰.三维片上网络TSV复用容错策略.电子测量与仪器学报,2013,27(3):229-235. |

| [35] | 欧阳一鸣,张一栋,梁华国,黄正峰.三维片上网络故障及拥塞感知的容错路由器设计.电子学报,2013,41(5):912-917. |

| [36] | 欧阳一鸣,何敏,梁华国,刘军,高妍妍.3D NoC中柔性可配置的高可靠路由器设计.电子测量与仪器学报,2014,28(3):306-313. |

| [37] | 欧阳一鸣,张一栋,梁华国,黄正峰,常郝.基于虚通道故障粒度划分的3D NoC容错路由器设计.计算机研究与发展,2014,51(9): 1993-2002. |

| [38] | 欧阳一鸣,韩倩倩,梁华国,黄正峰,汪秀敏.面向非全互连3D NoC可靠通信的分布式路由算法.计算机辅助设计与图形学学报, 2014,26(3): 502-510. |

| [74] | 郑飞.基于布图规划的三维片上网络功耗优化与仿真[硕士学位论文].武汉:武汉理工大学,2013. |

| [75] | 尹芝.3D NoC测试规划研究与实现.电子科技,2014,27(10):91-94. |

| [76] | 欧阳一鸣,刘蓓,齐芸.三维片上网络测试的时间优化方法.计算机研究与发展,2010,47(9):332-336. |

| [87] | 穆静.Torus拓扑结构的三维片上网络研究[硕士学位论文].上海:上海交通大学,2011. |

| [105] | 刘有耀,韩俊刚.超立方体双环互连网络及路由算法.计算机应用研究,2009,26(3):997-1000. |

| [138] | 秦云海,李丽.面向功耗的3DNoC路由算法研究[博士学位论文].南京:南京大学,2012. |

| [161] | 欧阳一鸣,韩倩倩,梁华国,黄正峰,汪秀敏.面向非全互连3DNoC可靠通信的分布式路由算法.计算机辅助设计与图形学学报,2014,26(3):502-510. |

| [163] | 胡哲琨,陈杰.基于层次化片上网络的混合多播路由算法.哈尔滨工程大学学报,2013,34(10):1327-1333. |

| [173] | 穆静,付卓宇,刘婷.片上网络中3D拓扑结构的性能评估.信息技术,2010,(5):70-73. |

| [174] | 贺旭,尤志强,邝继顺.三维超立方体片上网络拓扑结构性能分析.2011.中国科技论文在线. http://www.paper.edu.cn/releasepaper/content/201112-185 |

| [177] | 钱悦.片上网络演算模型及性能分析[博士学位论文].长沙:国防科学技术大学,2010. |

| [178] | 张媛媛,林世俊,苏厉,金德鹏,曾烈光.三维片上网络中torus与mesh拓扑结构的性能评估.清华大学学报,2011,51(12): 1777-1781. |

| [179] | 贺旭.超立方体结构在三维片上网络中的实现与性能分析[硕士学位论文].长沙:湖南大学,2012. |

| [180] | 江鹏.TSV功耗建模与3D NoC功耗分析[硕士学位论文].西安:西安电子科技大学,2012. |

| [183] | 黄岗.MPSoC互连网络功耗模型及其应用[硕士学位论文].西安:西安电子科技大学,2011. |

| [184] | 刘琪,李东生.片上网络的星型簇结构通信能耗研究.计算机应用研究,2012,29(6):2176-2179. |

| [188] | 王佳文.3D NoC关键技术研究[博士学位论文].南京:南京大学,2012. |

| [194] | 张振.基于3D-MESH的CMP片上网络映射方法研究[硕士学位论文].广州:广东工业大学,2012. |

| [195] | 杨微,张振,刘怡俊.基于改进粒子群的3D-Mesh CMP片上网络映射算法.计算机应用研究,2013,30(5):1345-1348. |

| [201] | 王佳文,李丽,易伟,潘红兵,张宇昂,侯宁,张荣.3D NoC映射问题的动态蚁群算法.计算机辅助设计与图形学学报,2011,23(9): 1614-1620. |

| [202] | 李东生,刘琪.面向通信能耗的3D NoC映射研究.半导体技术,2012,37(7):504-507. |

| [203] | 刘炎华.片上网络映射及路由器关键技术研究[博士学位论文].上海:华东师范大学,2013. |

| [218] | 许川佩,姚永兴.3D-NoC的测试端口选择优化.计算机应用研究,2015,32(3):1-5. |

| [219] | 徐欣.片上网络路由算法和映射算法研究[硕士学位论文].西安:西安电子科技大学,2010. |

| [220] | 董少周.NoC 路由算法及仿真模型的设计与研究[硕士学位论文].合肥:合肥工业大学,2009. |

| [221] | 杨懿泽.三维片上网络TSV与缓冲区容错技术研究[硕士学位论文].合肥:合肥工业大学,2013. |

| [224] | 汪凡.面向3D-Mesh片上网络服务质量保证机制研究[硕士学位论文].成都:电子科技大学,2012. |

| [229] | 王佳文,李丽,潘红兵,李伟,张荣.基于统计时分复用技术的三维片上网络.电子与信息学报,2012,10(34):2501-2507. |

| [233] | 王玉.多核处理器下三维片上存储结构研究[硕士学位论文].长沙:国防科学技术大学,2011. |

2016, Vol. 27

2016, Vol. 27