2 浙江大学 计算机科学与技术学院,浙江 杭州 310027;

3 浙江大学城市学院 计算机分院,浙江 杭州 310015

2 College of Computer Science and Technology, Zhejiang University, Hangzhou 310027, China;

3 School of Computer Science, Zhejiang University City College, Hangzhou 310015, China

为了满足计算需求,移动手持设备中多采用多核处理器,比如,nVIDIA的Tegra处理器和Intel的Atom处理器分别在平板电脑和智能手机中使用.与多核处理器相匹配,片上的缓存也越来越大,比如2M大小的L2缓存[1].另外,移动手持设备中的内存容量也在不断地增加,容量增加的缓存和内存带来的一个直接的后果就是,其能耗在系统能耗中的占比不断攀升.当前,存储器件的功耗也已经占到5%~30%[2, 3].ITRS2011报告中对未来手持消费电子设备的系统功耗进行预测,认为未来存储系统将消耗50%左右的总体能耗.手持移动设备一般是电池供电,与有线电源相比,电池的容量一般有限,制约着电子设备的使用时间,影响了客户的使用体验.虽然电池技术也在发展,但是远没有跟上手持设备对电量的需求.另一方面,有研究指出,IBM的中型服务器中,存储系统的能耗已经占了整个计算机系统的40%[4].电费已经成为像Google、亚马逊等网络公司的主要开销之一,这些网站服务器所需的电量只能由附近专门的电厂提供才能满足.因此,能耗是移动设备以及高性能计算系统中一个主要的设计指标,而存储系统的低功耗设计更是关键.

针对能耗问题,现有的存储系统也提供了一系列的硬件节能支持.比如,传统的DRAM内存采用分块的结构,在访问某数据时,只需激活该数据所在分块的电路,而不需要触发其他分块的电路,从而降低能耗.另外, DRAM内存的分块可处于多种不同的能耗状态:正常态和低功耗态.当内存块处于空闲状态时,它就可以切入低功耗状态,达到节能的目的.半导体晶体管的能耗主要分为静态功耗和动态功耗,静态功耗主要是由CMOS漏电流引起的功耗,传统的DRAM和SRAM存储器件由于其固有的存储特点,随着半导体工艺向深亚微米发展,其静态功耗在总功耗中所占的比例趋向于增加[5],已有的技术难以从根本上解决静态功耗问题.而新型的非易失性存储器件[6],比如Phase Change Memory(PCM)[7, 8]和Spin-Transfer Torque RAM(STT-RAM)[9],则具有非易失性、静态功耗低、密度大等优点.在非易失性存储器件中,数据的存储不依靠电容的充放电,而是通过改变内部晶体的状态从而改变自身电阻值的方式来存储数据,并且晶体的状态可以长时间保持,没有额外的功耗.因此,很多体系结构设计者提出用非易失性存储器件来代替传统的易失性存储器件.但非易失性存储器件也有自身固有的缺陷:写延时长、写能耗大和写寿命较短.而易失性存储器件的优点正好与非易失性器件的劣势互补,所以自然地,研究者考虑采用混合器件来构建低功耗的存储层次系统.

上述的硬件支持提供了节能的平台支持,但是要发挥出平台的潜力,就必须考虑软件的特性.存储系统结构设计的历史表明:要结合软件的属性,指导硬件结构的设计,才能更好地利用器件的优势.比如缓存这一结构,就是基于程序访问过程中的局部性特点,充分利用SRAM器件访问速度快的优势,从而达到系统性能的提升.同样地,在存储系统的低功耗设计中,对于程序访存规律的研究,有助于更有效地挖掘存储器件的低功耗硬件优势,规避弱势,促进低功耗存储技术的应用.本文对程序的访存模式作明确的定义,归纳程序访存模式的3个方面的内涵,并且结合已有的工作探讨程序访存模式在低功耗存储技术研究中的应用和意义,尤其是对缓存和内存.缓存和内存的低功耗技术在表面上差别很大,但是本质上都体现了程序访存模式3个方面内涵的应用.这也从一个侧面反映了计算机系统设计中软硬件相结合的特点.

本文第1节对现有的存储系统的组织架构、基本概念和已有的硬件节能支持作简要的概述.第2节主要描述本文对程序访存模式的定义和3个方面的内涵.第3节主要介绍程序访存模式在现有缓存和内存节能技术中的应用.第4节对未来可能的研究方向进行展望.第5节总结全文.

在介绍程序的访存模式之前,本节首先对当前计算机中的存储系统做一简要介绍,包括其基本概念.另外,本节还着重介绍了现有的硬件节能支持,包括新型的非易失性存储器件.

随着处理器性能的提升,存储层级系统也逐渐发展.例如,处理器在1980年是不带缓存的,但是到了2001年,处理器芯片内部通常有两级缓存,目前已经发展到三级缓存系统,并且缓存的容量已经比以往有巨大的增加,乃至于处理器上的面积基本都是缓存.另一方面,内存的容量也按照摩尔定律的规律增长,设计上的复杂性和容量的增大,使得存储系统的能耗和性能等问题日益显著,因此,存储层次的管理和控制就十分重要.

缓存中的数据主要以缓存块的方式组织,一般而言,一个缓存的大小为64字节,多个缓存块又组成一个缓存组.缓存管理主要涉及缓存块的查找、插入和替换操作,由于速度的要求,上述操作都由硬件完成.来自内存的缓存块会根据其物理地址的前半段定位目标缓存组,再在目标缓存组中找到空闲的缓存块,然后将缓存数据写入该缓存块,并且将地址的后半段写入到该缓存块的标签(tag)中,这样就完成了缓存块插入过程.在查找缓存块时,来自处理器的经过虚实地址转换后的数据地址的前半段用于定位目标缓存组,而地址的后半段则与目标缓存组中的各个缓存块的标签值比较,标签值匹配的即是目标缓存块.在缓存管理中,研究较多的是缓存块的替换问题,当某个缓存组已满但又有新的缓存块映射到当前这个缓存组时,就需要根据相应的替换策略将当前缓存组中的某个有效缓存块替换出去,从而腾出空间来接受新到的缓存块.替换策略主要就是决定当前缓存组中的哪个缓存块应该被替换出去.

内存比缓存大,所以其基本的组织单位物理页,要比缓存块大很多,一般大小为512KB,因此包含大量的缓存块.物理页是操作系统管理内存的基本单位,而内存硬件层面的基本组织单位是内存块(bank).每个内存块包括存储阵列和相关的逻辑电路,其中最重要的是行缓存器(row buffer).外界的读请求首先会定位到某个内存块,然后,目标数据会从存储阵列中首先读取到行缓存器,外界再通过I/O电路从行缓存器中读取数据.同样地,当写请求到达时,写更新的数据也会先写往行缓存器,然后再由行缓存器写到存储阵列中.传统的内存主要由DRAM实现,而DRAM属于易失性存储器件,即储存单元依靠电容上的电子存储数据,由于存在着漏电流,随着时间的流逝,电容上的电子会减少.为了保证存储单元上的电压的稳定,也即确保其中所存储的值,需要对DRAM存储单元进行周期性的刷新操作,也即充电操作.这样的周期性操作会带来额外的功耗,称为刷新功耗.

有研究指出,晶体管的静态功耗将以指数级的方式增长[10],使得系统设计者不得不正视静态功耗这一问题.研究静态功耗需要从器件本身入手.缓存和内存的基本器件分别是SRAM和DRAM,这两种器件都属于易失性器件,存在漏电流.虽然通过降低供电电压[11]以及从电路层面的优化[12, 13]可以在一定程度上缓解问题,但还是需要更好的技术和手段.最近出现的新型的非易失性存储器件,比如PCM和STT-RAM,则具有非易失性、静态功耗低、密度大和可扩展性强的优点.

相变存储器(phase change memory,简称PCM)是一种非易失性存储器,其信息载体为一种被称为GST (Ge2Sb2Te5)的相变材料.如图 1(a)所示,GST的上端连一个电极(electrode),下端通过一个加热元件(heating element)与下面的电极相连.当注入电流后,加热元件发热,GST相应地会在晶态和非晶态两种状态之间切换.两者对应的不同的电阻值恰好可以用于逻辑值“0”和“1”的存储.当GST处于任一状态时,能够持久地保持,所以存储的数据是非易失的.GST在两种状态时的阻值范围变化非常大,达到数个数量级,所以,也可以通过让一个存储单元表现出多级阻值来存储多于1位的信息,借此提高存储密度.

| Fig. 1 PCM cell, STT-RAM cell and MLC (multi-level cell) STT-RAM cell图 1 PCM,STT-RAM和多级STT-RAM的存储单元 |

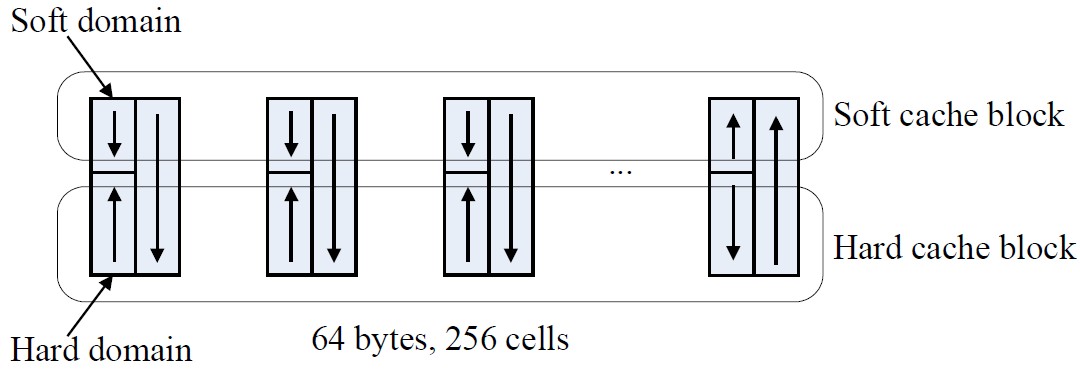

一个STT-RAM单元中主要包含的器件为Magnetic tunnel junction(MTJ),用于存储信息,每一个MTJ包含两个铁磁层(ferromagnetic layer),两者之间夹着一氧化物栅层(oxide barrier layer),通常是氧化镁,如图 1(b)所示.其中,磁化方向固定的铁磁层称为参照层(reference layer),另外一个磁化方向可变的就是自由层(free layer).磁化的变化通过注入电流来控制.在一个单级MTJ中,当参照层和自由层的磁化方向相同时,MTJ呈现低阻值状态,表示逻辑值为0;当两个层的磁化方向相反时,MTJ呈现高阻值状态,逻辑值为1.多级STT-RAM存储单元与单级STT-RAM存储单元的主要差别在于,多级STT-RAM的自由层分为被分成两个域(domain),每个域有不同的磁化特性,如图 1(c)所示.其中,软域(soft domain)的铁磁方向只要一个小电流值就可以改变,而另外一个硬域(hard domain)则需要一个较大的电流来改变铁磁方向.由于自由层被分成两个域,对应的每个多级MTJ可以存储两个位的信息.本文将硬域中存储的位信息称为硬位(hard bit),而将软域存储的位信息称为软位(soft bit).

现有的DRAM内存采用分块结构,并且分块可以在空闲时切入低功耗状态节能.但是,当出现对该内存块的新的访存请求时,内存块必须切回到正常态服务数据的读写请求.上述的分块和不同工作状态的内存硬件设计为上层的软件节能机制提供了支持,而上层的软件能对应用程序的各种运行信息有更好的把握,因此可以根据应用程序的特点,更好地发挥硬件节能技术的效果.除了分块和不同工作状态以外,内存的节能经常需要涉及到内存控制器.每一个对内存的数据读写请求,都需要通过内存控制器来处理.因此,内存控制器可以对内存中各个块的读写模式进行统计和观察,总结出一些访问模式,并且利用这些模式对内存数据的分配和映射做出有利节能的决策[14, 15, 16, 17].

PCM具有静态能耗低的优势,可以弥补DRAM静态功耗过大的缺陷,但是也有其自身固有的缺陷,比如写延时长、写能耗较大.表 1[18, 19]给出了DRAM和PCM以及SRAM和STT-RAM的写延时和写能耗的比较. PCM和STT-RAM的写延时要长4倍~6倍,STT-RAM的写能耗要比SRAM高7倍~8倍.另一方面,易失性存储器件的优点正好与非易失性器件的劣势相互补,所以自然地,可以考虑采用混合器件来构建低功耗的存储层次系统,比如采用SRAM和STT-RAM混合进行缓存设计[19, 20]、DRAM和PCM混合来构建内存[21, 22].这些混合设计的基本思想在于发挥易失性存储器写速度快和写能耗低的优势,利用非易失性存储器容量大和静态功耗低的优点,趋向于将写密集和频繁的数据分配或者迁移到存储器中的易失性存储器部分,从而使得大量的写操作花费的能耗最小化,达到节能目的.

| Table 1 Write latency and energy to different memories 表 1 不同存储器件的写能耗和写延时 |

本节主要介绍程序访存模式的定义,并从3个方面阐述其内涵.

定义1. 程序的访存模式是程序在访问存储器件时所体现出来的规律.

已有关于程序访存模式的定义均从特征代码块切入,例如代码中的数组操作估计程序中的访问热点[23],也有针对代码中的迭代代码段进行代码重构的[24, 25].本文定义的程序访存模式不局限于程序代码层次,更注重程序与存储器件之间的交互所体现的特征和规律.这里的规律从物理空间上看发生在3个位置:处理器访问缓存、缓存层次之间的相互访问以及最后一级缓存与内存之间.处理器一般以字的粒度进行读写,缓存层次中的访问和组织粒度以缓存块为单位,而内存中数据则以物理页为单位组织.各个层次间的访问粒度存在的差异导致了访存模式的空间特征.另外,数据的读写请求由处理器发起,然后逐级向下到缓存,进而到内存.访问的频繁度则是逐级递减,即大多数的读写访问请求会在缓存中的较高层级得到满足.这种访问频度的差别导致了访存模式的时间特征.最后,程序数据的本身存在着读写属性和频繁度的差别,由此导致程序访存模式的数据特征.以下对访存模式具有的空间特征、时间特征以及数据特征做详细的说明.

定义2. 访存模式的时间特征是指数据使用的频度和生命期.

所谓的频度是指数据最近是否会被使用,其使用的间隔一般是多久;生命期是指数据未来是否还会被使用,其对应的数据是否已无效.访存模式时间特征的典型应用就是缓存结构的出现以及缓存中的数据块替换策略的设计,比如最近最少使用(least recently used)替换策略和访问间隔预测(re-reference interval prediction)替换策略[26].一个缓存组中的各个缓存块在最近一段时间的使用顺序上总存在先后顺序,比如某个缓存块刚被访问而另一个则最近最长时间未被访问.可以认为,最近被访问的缓存块在未来很可能再被使用,而最近最长时间没有再被访问的缓存块则被认为未来也不太可能被访问.基于这样的时间特征,最近最少使用替换策略的操作就是:每次在替换缓存块时,都选择缓存组中的最近最长时间未被访问的缓存块.

定义3. 访存模式的空间特征是指空间局部性原理及特定存储粒度下的数据访问模式.

空间局部性具体指与当前被访问数据的地址相近的数据可能在最近的一段时间内也会被获得使用,其典型的应用就是体系结构中的数据预取技术.预取技术针对内存访问延时大,为了尽量少去访问内存,将内存块中的数据提前取到缓存中.在下次访问到该数据时,只需要从缓存中读取即可,不需要再去访问内存,从而提升性能.特定存储粒度下的数据访问模式是由于不同存储层级的粒度不同造成的,而存储粒度则是存储器中的数据组织单元,比如缓存中的组和块、内存中的分块和物理页.这些存储粒度下的访问模式主要指粒度中的数据在被访问时的不对称性,比如,对于内存块的绝大多数访问,都会落在少数的几个物理页中[27];处理器以字读写缓存中的缓存块时,会对缓存块中部分的字读写频繁,而对另外的字则读写较少;同一个缓存组中的不同缓存块,其中部分缓存块被频繁写,而另外的则可能很少被写.

定义4. 访存模式的数据特征是指数据的读写属性和读写频率.

具体而言,程序编译后的可执行代码一般被分成不同的数据段,包括数据段、代码段、堆、栈等,不同数据段中的数据就对应着不同的读写特性.比如,代码段中的数据主要以读为主,而堆和栈中的数据就有更加频繁的读写操作.另外,程序在编译阶段也可以获取关于变量的读写频率信息,也即获得关于数据变量的访存模式.典型应用是在编译阶段的程序数据到存储器时的优化映射.另外,数据特征也包括处理器在写更新数据时的特征.在写更新时,处理器新数据与旧数据的大多数值是相同的.这一数据模式的典型应用就是:在非易失性存储器中,可以通过删除冗余写操作来节能.

本节主要介绍程序访存模式在现有的低功耗存储技术中的应用,其中的技术主要针对缓存和内存,因为这两者占整个存储系统中能耗的绝大部分.表 2显示了缓存和内存节能技术所利用的访存特征,以及这些访存特征的具体表现形式.下面,本文将从缓存和内存两个方面做更具体、深入的介绍.

| Table 2 Comparison of cache and memory energy-efficient management 表 2 内存和缓存的节能技术对比 |

缓存弥补了处理器与内存之间的速度差异,提升了系统性能;但是容量增大的缓存也带来能耗的问题.而针对缓存的节能研究,主要应用程序访存过程中的空间、时间和数据特征,具体表现为如下的三者:

1) 缓存中不同粒度的访问频次不对称性:同一缓存组中的不同缓存块以及同一缓存块中的不同字块访问次数的不对称性,不同缓存块之间的读写次数的不对称性.

2) 缓存中的数据寿命比内存中的数据要短得多.另外,不同的缓存块之间的的寿命也存在着差异.

3) 缓存中的数据在数据更新阶段具有存在着大量的冗余更新以及特定的字符串频繁出现的特点.

从缓存的访问空间特征来说,不同缓存组和同一缓存组中的不同缓存块存在着访问不对称性[28, 29].比如,部分缓存组被密集访问,而部分缓存组很少被访问;有的缓存块写得频繁,有的缓存块则甚少被访问.缓存组使用的不对称性会导致缓存资源的浪费,而且影响系统性能的提升.在以往的SRAM缓存下,只能通过整合和管理缓存组间的资源[28, 29]提升系统性能,从而间接地达到节能.基于STT-RAM和SRAM的混合缓存器的出现,为直接利用缓存访问不对称性的节能技术提供了可能.非易失性STT-RAM存储器的优缺点刚好与SRAM互补,这种器件层次的互补性与缓存访存的不对称性相结合,成为后续相关节能技术的基础.

利用缓存组间以及组内的访问不对称,采用不同的材质按一定的比例来实现缓存组.比如,部分的缓存组采用SRAM来实现,部分的缓存组基于STT-RAM实现;同样地,在一个缓存组内部,也可以按一定的比例采用不同的存储材质来实现.在使用过程中,尽量将写访存密集的数据组分配到SRAM缓存组,利用SRAM动态写能耗低的特点节能;另一方面,尽量将写访问不密集的数据分配到STT-RAM缓存组,利用STT-RAM静态功耗低的优点节能.由于STT-RAM的密度大于SRAM,同样面积的混合缓存容量大于传统的SRAM缓存,因此降低能耗的同时也能提升性能.基于上述思想,文献[19]提出了以缓存组为基本单位的混合缓存设计,每个缓存组由少量的SRAM缓存块和大量的STT-RAM缓存块构成.然后,尽量将写频繁的数据块分配到SRAM缓存块中,将读频繁的数据块分配到STT-RAM缓存块中,并且提出一种低代价的全硬件机制,用来侦测哪些是写频繁的数据块,将这些数据块映射到SRAM缓存块中,并且把SRAM原有的对象迁移到STT-RAM缓存块中.文献[30]利用缓存组中的缓存块并不会都同时有效的特点,提出了通过过滤不必要的缓存路访问来降低缓存动态功耗的方法.该方法通过采用无效访问过滤器(invalid filer)来消除对无效数据的缓存路访问,从而达到节能.

研究者利用不同缓存块之间的读写属性差别,对多级STT-RAM缓存的结构进行重设计.每个多级STT- RAM单元包含两个域:一个硬域和一个软域,两个位的数据值分别存放在这两个域中.其中的硬域读得快,写得慢,而软域则正好相反.根据缓存块中的数据块的不同读写属性,文献[1]基于多级STT-RAM提出一种新的缓存块构建方式,即,从逻辑上将多个单元的软域整合在一起,形成软块(soft cache block),对应地,如图 2所示,将硬域整合成硬块(hard cache block).利用软块写速度快、写能耗低的特点,将写频繁的数据尽量存放到软块上去.同时,由于程序数据的写频繁度会发生变化,再引入数据迁移的策略,将变为写频繁的数据从硬块上迁移到软块;相应地,将软块上的变为写不频繁的数据迁移至硬块上,从而获得性能的提升和能耗的降低.

| Fig. 2 MLC STT-RAM cache block图 2 多级STT-RAM缓存块结构 |

除了缓存组内不同缓存块间的访存不对称性以外,同一缓存块的字间也存在着访存的不对称性.一般的缓存块大小为64字节,而处理器在访问缓存时以字为单位进行读写.处理器对部分的字会反复访问,而对部分的字则根本不访问,由此造成缓存块内字块访问的不对称性.文献[31]以字为单位,研究L2缓存块中的数据字的使用情况,发现很多缓存块中大部分的字都没有被使用.具体而言,缓存块中大概有75%的数据在缓存中一直没有被使用.作为利用该特征进行节能的两种可行途径:首先,考虑对不使用的字块进行提前替换,压缩数据块的大小,增加同样容量中的有效缓存的数量,提升性能,间接地达到节能;其次,既然缓存块中的很多数据没有被访问,就可以减少对这类数据的应用操作,达到节能.对于前者,文献[31]提出一种缓存块过滤技术,将缓存块中不会使用到的字剔除,意味着存储相同有用数据量的存储空间变小,从而间接达到节能的效果.对于后者,文献[32]根据缓存块中的很大一部分字不进行写更新的特点,提出选择性的写前读策略,达到降低非易失性缓存能耗的目的.主要想法在于对L1中的缓存块增加标志位,追踪其中的脏字.当L1中的缓存块写回到L2时,只对其中的脏字进行写前读策略,减少不必要的操作,从而节能.

缓存访问过程中的时间特征主要体现在缓存块的替换过程中.缓存中的数据持续被替换,意味着数据不会存放过长的时间.在这样的访存模式下,对存储器件的非易失性没有很高的要求,因为数据在存储器达到非易失性时间上限之前就已经被替换出去.这说明STT-RAM作为缓存时,其非易失性的特点没有太大意义.基于上述考虑,文献[33]提出了大幅度削弱STT-RAM非易失性而达到提升写性能、降低写能耗的基本思想.其主要方法是:通过减小MTJ中自由层的面积,并且辅助一简单的缓存重刷新机制来保存一些过早丢失的数据.采用该方法修改后的STT-RAM构成的缓存可以获得很好的性能能耗比.

针对缓存的多级结构,研究者研究了L1和L2两个层级之间的缓存访问模式,发现其中从L1替换到L2的缓存块并不会被再次使用;另一方面,将这些不会再被使用的缓存块写回到L2中需要消耗写能耗,尤其当L2属于非易失性存储器件时.因此,文献[34]提出采用计数器来预测缓存块的使用寿命.当预测到某L2缓存块已经达到使用寿命,不会再被使用时,对其的写更新操作会绕过L2,直接在下一级存储器更新.另外,研究者也关注L2中的缓存块的使用间隔,也即某缓存块间隔多久会被再次访问.根据这一L2的访存模式,文献[35]提出了一种基于智能预测的缓存块关闭机制.其主要思想是:如果有较大把握确定某个缓存块在一段时间内不会被使用,就可以将该缓存块关闭,从而达到降低静态能耗的目的.

缓存数据的数据特征主要体现在缓存数据值的模式和更新过程,其中,值模式研究的一个方面是统计其中的两位数据组“00”,“01”,“10”和“11”等出现的比例.每个多级STT-RAM单元存储两位信息,文献[36]中观察应用在缓存块中的数据,前述4个字符的比例并不均衡,存在很大的偏差.基于该访存模式以及结合多级STT-RAM的写操作的状态转换图,文献[36]提出一种优化的编码方式(encoding scheme),将字符表达的信息进行重新映射,比如,把字符“01”映射为“00”,也就是当前缓存块存放的字符“00”,其真实值为“01”.通过上述的重新编码方式,可以在一定程度上优化数据的写过程,获得性能和能耗上的收益.

通过对缓存块的数据值更新过程的研究,研究者发现缓存块写回操作中普遍存在的模式:缓存块要更新的数值与原有的数值绝大多数相同.基于上述的数据写模式以及非易失性缓存写能耗高的特点,文献[37, 38, 39]对非易失性器件构建的缓存器提出写前读技术.该技术的核心思想是:在缓存块的数据更新之前,将其中的原有数据读出,并且按位与新数值进行比较;然后,只对其中前后数值不同的数据位进行写更新操作.这种去冗余的操作,大致可以减少80%~90%的写操作,极大地降低了非易失性缓存的写能耗,达到节能.在此基础上,文献[37]提出两个数据的汉明距离(hamming distance)的概念,汉明距离标志着两个数据之间的异同程度,距离小就意味着相似度高,也就意味着不同的数据位少.文献[39]在汉明距离的基础上,进一步引入反转汉明距离的概念.类似于写前读策略,文献[38]提出一种降低冗余写操作的方法.该方法利用写操作和读操作在前半阶段的相似性对写电路进行修改,在写操作的早期将数据从STT-RAM单元中读出,并与新数据进行比较,如果两者的值相同,那么后续的写操作就会停止,也就是说提前终止写操作,从而达到节能.

与缓存相比,内存的访问频度不高,但是其绝对存储容量更大,吞吐量更高,数据的保存时间更长,这些使得内存消耗的能耗在系统中举足轻重.可以用于内存节能的访存模式主要体现为:1) 内存访问中不同层次的局部性,从行缓存器到物理页;2) 内存中数据读写属性差异以及重要性的差别.

一个内存条包含多个rank,每个rank又包含多个块(bank).数据在内存块中以数据阵列(data array)的形式存储,如图 3所示.读数据时,数据阵列中的数据以数据行(row)为单位先传输到行缓存器,再通过读写I/O电路传输到外面;写数据时,操作过程刚好相反.当某读访问的数据不在当前的行缓存器中时,则需要写回当前的行缓存器中的数据,并且将目标数据所在的行读到行缓存器中进行操作.某程序中有越多的数据访问可以在当前的行缓存器中得到满足,就认为该程序的行时间局部性(row temporality locality)越好.类似地,可以在混合内存系统中利用上述的行时间局部性对混合内存系统进行节能操作.文献[40]研究了应用程序访问内存块中的行缓存器时的命中率情况,其中,行局部性(row locality)高的行,其相应的命中率高,而行局部性低的行命中率低.另一方面,基于DRAM的内存块和基于PRAM(PCM random access memory)的内存块访问行缓存器的时间延迟基本相同,但是当没有在行缓存器命中时,需从存储阵列中读取数据到行缓存器,两者的延时就存在显著差别.其中,PRAM在这个方面的延时就显得更加显著.根据上述的行缓存访存模式以及DRAM和PRAM的器件特点,文献[40]针对DRAM/PRAM混合内存提出基于行局部性的数据分配策略,将其中行局部性高的数据分配到PRAM内存块,而将行局部性低的数据分配到DRAM内存块.如此,既可以利用PRAM静态能耗低的优势,又可以利用DRAM在行缓存器访问缺失时,其重载数据延时低的优势,兼顾能耗和性能.与缓存类似,除了行时间局部性以外,对应的还有行空间局部性,即,大多数的数据访问集中在行缓存器中的特定位置.利用行空间局部性节能的一般思路是:将整个行缓存器进行分割,每次只使用特定部分,减少不必要的电路激活,从而节能[41].

| Fig. 3 Memory bank structure图 3 内存分块的结构 |

程序的数据以物理页为单位分配到不同的内存块上,并且对内存的访问绝大多数集中在少数物理页中.文献[27]研究了程序对物理页的读写访问情况,发现绝大多数的读写访问落到少数的物理页上.具体而言,大约90%的内存读写访问落到1.5%~14.3%的物理页上.要利用这种物理页访问的不均衡性节能,需要结合内存的分块结构.程序对物理页的访问最终落实到对内存块的访问.另一方面,内存块在空闲时段可进入低功耗状态节能.其处于低功耗状态的时间越久,相应的节能效果越佳.当对应的内存访问到来时,内存块必须由低功耗状态切换到正常工作状态来服务访问请求.一个重要的问题是:让尽量多的内存块尽量久地不受内存访问打扰,处于低功耗状态.结合上述的内存页访问不均衡性,既然少量的物理页承担绝大多数的内存访问,那么将这些物理页聚集到同一内存块.该内存块处于正常态服务于大多数内存访问,而其他的内存块则处于低功耗状态进行节能.基于这一思路,文献[27]提出了对物理页的迁移策略,即将少数的访问密度高的物理页迁移到同一个内存块上,像这样,其他内存块就可以处于低功耗状态,从而节能.在DRAM/PRAM混合内存架构下,利用上述的物理页访问不均衡性的基本思路是:尽量将写访问频繁地物理页安排在DRAM端,利用其写能耗低的优点;将写访问一般的物理页放置在PRAM,利用PRAM容量大、静态功耗低的优点.根据这一思路,文献[42]根据PRAM和DRAM各自的特点,提出了以PRAM作为大容量主存、以DRAM作为主存缓存的混合内存设计.这一结构结合了DRAM访问速度快和PRAM密度高、静态功耗低的优点.与纯粹的PRAM内存相比,该结构可以加速3倍、减少80%的页错误以及提升PRAM近3倍的写寿命.另外,文献[22, 43]研究混合内存下的页缓存设计,分别提出优化的页缓存策略,将写密集的数据页分配到DRAM区域,而将读密集的数据页分配到PRAM区域,从而更好地发挥两者的优势.文献[44]就PRAM和DRAM的混合架构提出了一种基于硬件的物理页分配策略.该策略依赖内存控制器对访问流监控,并且引入内存块关于访问频繁度的排序机制,根据排序结果,提出一种在PRAM和DRAM之间迁移物理页的策略.该迁移策略不仅考虑物理页的写访问频繁度,而且考虑物理页的访问密度,从而在优化PRAM写能耗的同时,还兼顾到了性能.

另外,如果可以获得物理页在某内存块上的访问模式,就能利用更多的内存块能够处于低功耗状态的机会,而且不用担心因此而损失性能.操作系统的一种重要任务是管理共享资源,比如内存和处理器时间.操作系统对应用程序进行调度,使得不同的程序分时共享处理器,这就导致程序在内存访问上的时间特征,即,只有当前程序占用处理器的这段时间,内存才会得到访问;在程序挂起期间,其不产生内存访问请求.结合程序调度过程和程序数据到内存块的映射关系,预判某个内存块在未来的使用情况,针对其空闲时段利用低功耗状态节能.基于上述思路,文献[45]中提出一种基于操作系统调度器的内存节能方法.该方法通过操作系统中的内存管理服务程序,追踪每个程序的数据在内存中的分布,比如某个程序的数据具体分布在哪些内存分块上.获得上述的信息后,操作系统可以在调度运行某个程序开始之际,将该程序不会访问到的内存分块切入低功耗状态,从而达到节能.文献[46, 47]对上述基于调度的内存节能方法进行了扩展,其中,文献[46]考虑了内存块切换所导致的能耗,提出了内存块切换最小化的节能调度策略,减少内存块的状态切换次数,从而达到节能的目的;文献[47]考虑多核平台下的多个任务运行时的内存块访问冲突问题,提出多核下的任务调度策略,使得每个任务调度时间片下尽量多的内存块可以处于低功耗状态,从而达到节能的目的.

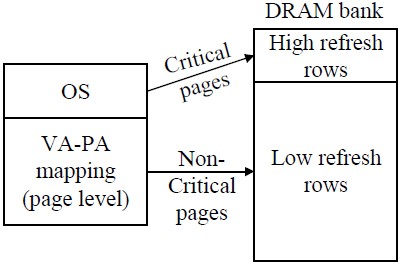

与缓存相比,内存的数据容量巨大,其中的数据蕴含不同的属性,比如,数据有不同的重要性和不同的读写属性.数据的重要性主要体现在该数据的正确性对程序是否可以稳定运行的影响,根据影响的程度,程序中的数据可以分为关键数据[48, 49]和非关键数据.程序对于关键数据出错的容忍能力较弱,而非关键数据中即使出现较多错误,对程序的运行影响也有限.内存中的数据存储于每个DRAM单元的电容中,由于漏电流的存在,每个DRAM单元需要及时地周期性刷新,保证所存储的数据的正确性.但是刷新的代价就是额外的能耗,已经有研究显示[50],数据刷新能耗在内存能耗中的占比越来越大.降低数据刷新能耗的一个直接方法就是延长刷新周期,进而减少刷新次数,带来的后果是存储单元上的数据容易出现错误.延长数据刷新周期时,既然错误的出现无法避免,问题就在于如何让错误可控.可以考虑的思路主要有:错误难免,就是让错误发生在无关紧要的地方.文献[51]提出了一种应用层的技术,用于减小存储器的刷新功耗.该技术区分应用程序中的关键数据和非关键数据,并且将这两部分数据放置在内存中的不同区域,具体的操作流程如图 4所示.对于包含关键数据的区域,内存的刷新频率不变;而对于那些存放非关键数据的区域,则采用相对较低的刷新频率.由于非关键数据对于程序的运行并不十分重要,因此上述的方法可以在保证程序正常运行的情况下降低刷新功耗,达到节能的目的.

| Fig. 4 OS directed program data allocation to DRAM bank图 4 OS指导下的程序数据到内存的分配 |

对于数据变量的读写属性,其中程序的各个数据段的属性,可以为混合PRAM/DRAM内存做出数据映射的指导.简单而言,可以将程序中的代码段映射到PRAM器件中.因为代码段只有读操作,没有写操作;而PRAM的读功耗低,但写功耗却很高.另外,堆数据段中的数据由于频繁地申请和释放的缘故,其生命期较短,即数据块被释放而无效.因此,该模式可以用来指导最后一级缓存对非易失性器件内存的写回操作,若某堆中的数据块被释放且位于非易失性存储器中,那么最后一级缓存中再对该数据块进行写操作就没有意义,可以剔除以节能.

结合当前软件和硬件方面的一些新进展,未来对于应用程序的访存模式的研究,依然对新架构下的存储系统的低功耗设计有指导意义.本节列举未来可能的研究方向:

(1) 新型应用程序的访存模式研究

目前的应用程序访存模式的研究对象主要是标准测试程序集SPEC2000/2006,SPLASH和PARSEC,对这些程序集的访存模式已有很好的研究,但是对于近期新出现的应用程序,我们对其访存模式所知道的就比较有限.比如,美国国防部高级研究计划局(DARPA)提出开发新一代的面向信息认知处理的体系结构(architecture for cognitive information processing),其面向的信息认知处理算法包括搜索、概率推理、基于知识的推理和机器学习等.这些算法有着巨大的商业应用价值,比如在疾病诊断、数据挖掘、证券市场、多媒体以及生物信息学等.但是当前,我们对这些负载的访存模式理解的十分有限,未来需要对这类应用程序的访存行为进行深入研究.另外,当前智能终端大量普及,其上所运行的应用程序以网络类和娱乐类为主,对于这些应用程序的访存模式也缺少相应的研究.

(2) GPGPU下的访存模式研究

目前,计算机领域中的一个重要方面就是提升计算的并行性,其中的一个重要进展就是开发数据并行性的GPGPU结构.GPGPU与CPU相比具有更为强大的计算能力,并且其计算能力的提升速度也远快于CPU,每年的速度提升大概是1.7倍~2.3倍[52],快于CPU的1.4倍,因此被广泛用于计算需求量大的场景[53].伴随着计算能力的提升,GPGPU的内存数据访问也十分可观,比如,NVIDIA GeForce 7900 GTX可以达到51.2GB/s的内存访问带宽[52].当前,针对GPGPU的节能存储研究较少,即使有,也集中于计算方面[54],并且对运行在GPCPU上的应用程序的访存行为的研究也很少.另一方面,GPGPU运行时的能耗远大于CPU,因此,未来降低其存储系统的能耗是一个重要的课题.

(3) 3D存储器对访存模式的影响

存储系统的访问延时是一个重要的研究问题.为了缩小访问延时,人们考虑采用3D堆叠的结构来构建内存系统.采用3D堆叠结构后,内存之间不再只是在二维结构的访问关系,而是可以进行垂直方向的数据读写访问,这样就大大缩短了单元之间的距离,因此可以有效降低访问延迟.文献[55, 56]提出了3D堆叠DRAM来构建大容量的缓存结构.在这种新型的缓存组织结构中,程序的访存模式将会呈现什么样特点?已知的访存模式可以如何帮助3D新型缓存的低功耗设计?另外还可以考虑的一个方向是3D堆叠结构和非易失性存储器件的结合:如何将3D的结构优势和非易失性存储器密度高、静态功耗低的优势有机地结合起来?如何规避3D结构的散热问题?如何在3D结构中解决非易失性存储器件的写能耗和延时问题?

未来存储系统的能耗在整个计算机系统中的能耗占比还将提升,所以,存储系统的低功耗设计依旧是一个热点的研究问题.为了更好地挖掘现有存储器件的节能潜力,基于程序访存模式的低功耗存储技术将被广泛使用.对于程序访存模式的深入理解,已经指导人们研发各种存储节能技术.这一现象充分体现了计算机系统设计中的软硬件设计的协同效应.随着新型的计算机架构(比如GPGPU和3D存储器)和程序集的出现,结合程序访问模式进行存储系统低功耗技术研究的方式还将继续.

本文回顾了已有的各种低功耗存储技术,对技术的动机和依据进行了梳理和总结,发现程序访问存储器时的规律性指导了很多低功耗技术的设计.本文给出程序访存模式的概念定义,归纳访存模式的3个方面的内涵,并且进一步详细地介绍了程序的访存模式在片上缓存和主存低功耗技术中的应用.最后,本文展望了未来结合访存模式进行低功耗存储系统研发的可能方向.

| [1] | Jiang L, Zhao B, Zhang YT, Yang J. Constructing large and fast multi-level cell STT-MRAM based cache for embedded processors. In: Proc. of the 49th Annual Design Automation Conf. New York: ACM Press, 2012. 907-912 . |

| [2] | Carroll A, Heiser G. An analysis of power consumption in a smartphone. In: Proc. of the 10th Annual USENIX Technical Conf. Berkerly: USENIX Association Berkeley, 2010. 21-30. |

| [3] | Viredaz MA, Wallach DA. Power evaluation of a handheld computer. IEEE Microarchitecutre, 2003,23(2):66-74 . |

| [4] | Lefurgy C, Rajamani K, Rawson F, Felter W, Kistler M, Keller TW. Energy management for commercial servers. Journal of Computer, 2003,36(12):39-48 . |

| [5] | Venkatachalam V, Franz M. Power reduction techniques for microprocessor systems. ACM Computing Survey, 2005,37(2): 195-237 . |

| [6] | Xue CJ, Zhang YT, Chen YR, Sun GY, Yang JJ, Li H. Emerging non-volatile memories: Opportunities and challenges. In: Proc. of the 7th IEEE/ACM/ IFIP Int’l Conf. on Hardware/Software Codesign and System Synthesis. New York: ACM Press, 2011. 325-334 . |

| [7] | Sun GY, Zhang YJ, Wang Y, Chen YR. Improving energy efficiency of write-asymmetric memories by log style write. In: Proc. of the 18th Annual Symp. on Low Power Electronics and Design. New York: ACM Press, 2012.173-178 . |

| [8] | Chen J, Chiang RC, Huang HH, Venkataramani G. Energy-Aware writes to non-volatile main memory. ACM SIGOPS Operating Systems Review, 2011,45(1):48-52 . |

| [9] | Hosomi M, Yamagishi H, Yamamoto T, Bessho K, Higo Y, Yamane K, Yamada H. A novel nonvolatile memory with spin torque transfer magnetization switching: Spin-RAM. In: Proc. of the 2005 IEEE Int’l IEDM Technical Digest electron Devices Meeting. Piscataway: IEEE Press, 2005.459-462 . |

| [10] | Diao ZT, Pakala M, Panchula A, Ding YF, Apalkov D, Wang LC, Chen E, Huai YM. Spin-Transfer switching in MgO-based magnetic tunnel junctions. Journal of Applied Physics, 2006,99(2):213-223 . |

| [11] | Qin HF, Cao Y, Markovic D, Vladimirescu A, Rabaey J. SRAM leakage suppression by minimizing standby supply voltage. In: Proc. of the 5th Int’l Symp. on Quality Electronic Design. Piscataway: IEEE Press, 2004.55-66 . |

| [12] | Yang SH, Babak F, Powell MD, Kaushik B, Roy K, Vijaykumar TN. An integrated circuit/architecture approach to reducing leakage in deep-submicron high-performance I-caches. In: Proc. of the 7th Int’l Symp. on High-Performance Computer Architecture. Piscataway: IEEE Press, 2001. 147-158 . |

| [13] | Zhang G, Hu WW. Leakage power optimization in high performance general-purpose microprocessor design. Chinese Journal of Computers, 2006,29(10):1764-1771 (in Chinese with English abstract). http://cjc.ict.ac.cn/qwjs/view.asp?id=2215 |

| [14] | Luz VDL, Kandemir M, Kolcu I. Automatic data migration for reducing energy consumption in multi-bank memory systems. In: Proc. of the 39th Annual Symp. on Design Automation Conf. New York: ACM Press, 2002.213-218 . |

| [15] | Lyuh CG, Kim T. Memory access scheduling and binding considering energy minimization in multi-bank memory systems. In: Proc. of the 41st Annual Conf. on Design Automation. New York: ACM Press, 2004.81-86 . |

| [16] | Zhang L, Qiu MK, Sha EHM, Zhuge QF. Variable assignment and instruction scheduling for processor with multi-module memory. Journal of Microprocessor and Microsystem, 2011,35(3):308-317 . |

| [17] | Qiu MK, Guo MY, Liu MQ, Xue CJ, Yang LT, Sha EHM. Loop scheduling and bank type assignment for heterogeneous multi- bank memory. Journal of Parallel and Distributed Computing, 2009,69(6):546-558 . |

| [18] | Zhou P, Zhao B, Yang J, Zhang YT. A durable and energy efficient main memory using phase change memory technology. SIGARCH Computer Architecture News, 2009,37(3):14-23 . |

| [19] | Jadidi A, Arjomand M, Sarbazi-Azad H. High-Endurance and performance-efficient design of hybrid cache architectures through adaptive line replacement. In: Proc. of the 17th IEEE/ACM Int’l Symp. on Low-Power Electronics and Design. New York: ACM Press, 2011. 79-84. |

| [20] | Wu XX, Li J, Zhang LX, Speight E, Rajamony R, Xie Y. Hybrid cache architecture with disparate memory technologies. ACM SIGARCH Computer Architecture News, 2009,37(3):34-45 . |

| [21] | Liu TT, Zhao YC, Xue CJ, Li MM. Power-Aware variable partitioning for DSPs with hybrid PRAM and DRAM main memory. In: Proc. of the 48th Design Automation Conf. New York: ACM Press, 2011.405-410 . |

| [22] | Seok H, Park Y, Park KH. Migration based page caching algorithm for a hybrid main memory of DRAM and PRAM. In: Proc. of the 2011 ACM Symp. on Applied Computing. New York: ACM Press, 2011.595-599 . |

| [23] | Grun P, Dutt N, Nicolau A. APEX: Access pattern based memory architecture exploration. In: Proc. of the 14th Int’l Symp. on System Synthesis. New York: ACM Press, 2001.25-32 . |

| [24] | Jang B, Mistry P, Schaa D, Dominguez R, Kaeli D. Data transformations enabling loop vectorization on multithreaded data parallel architectures. In: Proc. of the 15th ACM SIGPLAN Symp. on Principles and Practice of Parallel Programming. New York: ACM Press, 2010.353-354 . |

| [25] | Kandemir M, Yemliha T, Son SW, Ozturk O. Memory bank aware dynamic loop scheduling. In: Proc. of the Design, Automation Test in Europe Conf. New York: ACM Press, 2007. 1-6 . |

| [26] | Jaleel A, Theobald KB, Jr. Steely SC, Emer J. High performance cache replacement using re-reference interval prediction. In: Proc. of the 37th Annual Int’l Symp. on Computer Architecture. New York: ACM Press, 2010.60-71 . |

| [27] | Huang H, Shin KG, Lefurgy C, Keller T. Improving energy efficiency by making DRAM less randomly accessed. In: Proc. of the 2005 Int’l Symp. on Low Power Electronics and Design. New York: ACM Press, 2005.393-398 . |

| [28] | Qureshi MK, Thompson D, Patt YN. The V-way cache: Demand based associativity via global replacement. In: Proc. of the 32nd Annual Int’l Symp. on Computer Architecture. New York: ACM Press, 2005.544-555 . |

| [29] | Rolán D, Fraguela BB, Doallo R. Adaptive line placement with the set balancing cache. In: Proc. of the 42nd Annual IEEE/ACM Int’l Symp. on Microarchitecture. Piscataway: IEEE Press, 2009.529-540 . |

| [30] | Fan LJ, Xu YC, Shi WS, Fan DR, Lou J. Hybrid approach of filtering unnecessary way access for set-associative caches. Chinese Journal of Computers, 2013,36(4):799-808 (in Chinese with English abstract). http://cjc.ict.ac.cn/qwjs/view.asp?id=3833 |

| [31] | Qureshi MK, Suleman MA, Patt YN. Line distillation: Increasing cache capacity by filtering unused words in cache lines. In: Proc. of the 2007 IEEE 13th Int’l Symp. on High Performance Computer Architecture. Piscataway: IEEE Press, 2007.250-259 . |

| [32] | Zhang TF, Chen TZ, Wu JZ, Qu YT. A selective read-before-write scheme for energy-aware spin torque transfer RAM cache design. Journal of Circuits, Systems, and Computers, 2013,22(5):234-244 . |

| [33] | Smullen CW, Mohan V, Nigam A, Gurumurthi S, Stan MR. Relaxing non-volatility for fast and energy-efficient STT-RAM caches. In: Proc. of the 2011 High Performance Computer Architecture. Piscataway: IEEE Press, 2011.50-61 . |

| [34] | Kharbutli M, Solihin Y. Counter-Based cache replacement and bypassing algorithms. IEEE Trans. on Computers, 2008,57(4): 433-447 . |

| [35] | Abella J, González A, Vera X, O’Boyle MFP. IATAC: A smart predictor to turn-off L2 cache lines. ACM Trans. on Architecture and Code Optimization, 2005,2(1):55-77 . |

| [36] | Chen YR, Wong WF, Li H, Koh CK. Processor caches built using multi-level spin-transfer torque RAM cells. In: Proc. of the 2011 Int’l Symp. on Low Power Electronics and Design. New York: ACM Press, 2011.73-78 . |

| [37] | Joo Y, Niu DM, Dong XY, Sun GY, Chang N, Xie Y. Energy- and endurance-aware design of phase change memory caches. In: Proc. of the 13th Int’l Conf. on Design, Automation and Test in Europe. New York: ACM Press, 2010.136-141 . |

| [38] | Zhou P, Zhao B, Yang J, Zhang YT. Energy reduction for STT-RAM using early write termination. In: Proc. of the 18th Int’l Conf. on Computer-Aided Design. New York: ACM Press, 2009.264-268 . |

| [39] | Nigam A, Smullen IV CW, Mohan V, Chen E, Gurumurthi S, Stan MR. Delivering on the promise of universal memory for spin-transfer torque ram (STT-RAM). In: Proc. of the 17th IEEE/ACM Int’l Symp. on Low-Power Electronics and Design. New York: ACM Press, 2011.121-126 . |

| [40] | Yoon HB, Meza J, Ausavarungnirun R, Harding RA, Mutlu O. Row buffer locality aware caching policies for hybrid memories. In: Proc. of the 2012 IEEE 30th Int’l Conf. on Computer Design. New York: ACM Press, 2012.337-344 . |

| [41] | Gulur N, Manikantan R, Mehendale M, Govindarajan R. Multiple sub-row buffers in DRAM: Unlocking performance and energy improvement opportuniteies. In: Proc. of the 26th ACM Int’l Conf. on Supercomputing. New York: ACM Press, 2012.257-266 . |

| [42] | Qureshi MK, Srinivasan V, Rivers JA. Scalable high performance main memory system using phase-change memory technology. In: Proc. of the 36th Annual Int’l Symp. on Computer Architecture. New York: ACM Press, 2009.24-33 . |

| [43] | Seok H, Park Y, Park KW, Park KH. Efficient page caching algorithm with prediction and migration for a hybrid main memory. SIGAPP Applied Computing Review, 2011,11(4):38-48 . |

| [44] | Ramos L, Gorbatov E, Bianchini R. Page placement in hybrid memory systems. In: Proc. of the Int’l Conf. on Supercomputing. New York: ACM Press, 2011. 85-95 . |

| [45] | Delaluz V, Sivasubramaniam A, Kandemir M, Vijaykrishnan N, Irwin MJ. Scheduler-Based DRAM energy management. In: Proc. of the 39th Annual Symp. on Design Automation Conf. New York: ACM Press, 2002.697-702 . |

| [46] | Zhang TF, Yu LC, Chen TZ, Chen H. Process scheduling-based energy management for bank-aware memory system. Journal of Information & Computational Science, 2013,10(2):4007-4016. |

| [47] | Zhang TF, Chen TZ. Process scheduling based memory energy management for multi-core mobile devices. IEICE Trans. on Fundamentals of Electronics, Communications and Computer Sciences, 2012,10(2):1700-1707. |

| [48] | Pattabiraman K, Grover V, Zorn BG. Samurai: Protecting critical data in unsafe languages. In: Proc. of the 3rd ACM SIGOPS/ EuroSys European Conf. on Computer Systems. New York: ACM Press, 2008.219-232 . |

| [49] | Carbin M, Rinard M. Automatically identifying critical input regions and code in applications. In: Proc. of the 19th Int’l Symp. on Software testing and Analysis. New York: ACM Press, 2010.37-48 . |

| [50] | Alizadeh M, Javanmard A, Chuang ST, Iyer S, Lu Y. Versatile refresh: Low complexity refresh scheduling for high-throughput multi-banked eDRAM. In: Proc. of the 12th ACM SIGMETRICS/PERFORMANCE Joint Int’l Conf. on Measurement and Modeling of Computer Systems. New York: ACM Press, 2012.247-258 . |

| [51] | Liu S, Pattabiraman K, Moscibroda T, Zorn BG. Flikker: Saving DRAM refresh-power through critical data partisioning. ACM SIGARCH Computer Architecture News, 2011,39(1):213-224 . |

| [52] | Owens JD, Luebke D, Govindaraju N, Harris M, Krüger J, Lefohn AE, Purcell TJ. A survey of general-purpose computation on graphics hardware. Computer Graphics Forum, 2007,26(1): 80-113 . |

| [53] | Zhou L, Han WB, Zhu WH, Wang Z. Improvement and efficient implementation of differential attack algorithm to MDx on GPGPU. Chinese Journal of Computers, 2010,33(7):1177-1182 (in Chinese with English abstract). http://cjc.ict.ac.cn/qwjs/view. asp?id=3121 |

| [54] | Lin YS, Yang XJ, Tang T, Wang GB, Xu XH. A GPU low-power optimization based on parallelism analysis model. Chinese Journal of Computers, 2011,34(4):705-716 (in Chinese with English abstract). http://cjc.ict.ac.cn/qwjs/view.asp?id=3371 |

| [55] | Loh GH, Hill MD. Efficiently enabling conventional block sizes for very large die-stacked DRAM caches. In: Proc. of the 44th Annual IEEE/ACM Int’l Symp. on Microarchitecture. Piscataway: IEEE Press, 2011.454-464 . |

| [56] | Qureshi MK, Loh GH. Fundamental latency trade-off in architecting DRAM caches: Outperforming impractical SRAM-tags with a simple and practical design. In: Proc. of the 2012 45th Annual IEEE/ACM Int’l Symp. on Microarchitecture. Piscataway: IEEE Press, 2012.235-246 . |

| [13] | 张戈,胡伟武.高性能通用处理器中的漏电功耗优化.计算机学报,2006,29(10):1764-1771. http://cjc.ict.ac.cn/qwjs/view.asp?id= 2215 |

| [30] | 范灵俊,徐远超,施巍松,范东睿,娄杰.针对组相联缓存的无效缓存路访问混合过滤机制研究.计算机学报,2013,36(4):799-808. http://cjc.ict.ac.cn/qwjs/view.asp?id=3833 |

| [53] | 周林,韩文报,祝卫华,王政.MDx差分攻击算法改进及GPGPU上的有效实现.计算机学报,2010,33(7):1177-1182. http://cjc.ict.ac. cn/qwjs/view.asp?id=3121 |

| [54] | 林一松,杨学军,唐滔,王桂彬,徐新.一种基于并行度分析模型的GPU功耗优化技术.计算机学报,2011,34(4):705-716. http://cjc. ict.ac.cn/qwjs/view.asp?id=3371 |

2014, Vol.25

2014, Vol.25